基于DSP、DDS和ARM雷达中频信号模拟器研究

雷达信号模拟器是模拟技术与雷达技术相结合的产物。它通过模拟的方法产生雷达回波信号,以便在实际雷达系统前端不具备的条件下对雷达系统后级进行调试。随着数字技术的进步,高速、超大规模集成电路的使用,雷达信号模拟系统正朝着灵活、通用的方向发展。笔者设计了一种基于PC+ARM+DSP+DDS体系结构的能家长雷达中频信号模拟器,介绍了该系统的硬件设计,并以模拟相参数脉冲雷达动目标信号为例,介绍了本系统的应用。

本文引用地址:http://www.eepw.com.cn/article/257430.htm1 系统结构设计

现代雷达信号模拟的设计偏重于运用数字化方式实现,随着实时数字信号处理技术的发展,PC+DSP+D/A的体系结构成了雷达模拟器实现的主要方式。直接数字频率合成技术(DDS)以其在频率捷变速度、相位连续性、相对带宽、高分辨率以及集成化等方面的优异性能,成为现代频率合成技术中的佼佼者,同时也为雷达中频信号模拟的实现方式提供了新的选择。

本设计采用PC+ARM+DSP+DDS的体系结构。PCM机对目标及环境进行建模、运算,生成雷达中频信号仿真数据库,DSP根据模拟的雷达实时状态及目标、环境的实时特性,进行数据调度、运算和处理,最后形成控制DDS所需的调幅、调相、调频等控制字,通过DDS产生雷达中频模拟信号。

由于对模拟器通用性的考虑,PC机与DSP间的通信,希望不仅能实时改变雷达模拟信号的参数,还可以适应不同雷达体制和不同信号处理机的具体要求,方便加载新的程序。虽然通过PCI(或CPCI)能实现程序加载,并且传输速率快,但不能脱机工作,且插拔麻烦,不能用于笔记本调试。本设计采用ARM作为主控模块,控制USB接口器件和DSP的主机口,完成程序的加载和参数的实时设置。

2 硬件电路的设计与实现

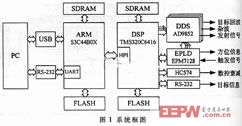

本系统主要包括以ARM为核心的主控模块,以DSP为核心的实时数据处理模块,以DDS为核心的信号生成模块,以及包括USB、RS-232和锁存器等的通信模块和电源系统,其系统框图如图1所示。

2.1 主控模块

系统主控模块负责控制和协调各种工作。ARM采用Samsung公司生产的S3C44B0X微处理器,通过集成锁相环倍频系统主频可达66MHz,最大外部存储空间256MB,片上资源丰富,外围控制能力强,性价比高。由它控制USB模块接收PC机计算生成的雷达模拟信号的数据及代码,控制主机口加载DSP,控制UART实现工作状态在PC机上的实时显示。

2.2 实时数据处理模块

实时数据处理模块利用PC机生成的雷达信号模拟数据,根据设定的雷达工作状态及目标、环境的实时动态计算DDS的控制字,控制三片DDS输出雷达模拟信号。同时通过串口与信号处理机交换信息,通过锁存器向处理板提供控衰减控制信号。

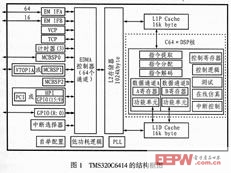

DSP采用TI公司C6000系列中的TMS320C6416,系统时钟达600MHz,数据处理速率可达4800MIPS。提供32/16bit主机口,具有两个独立的外部存储器接口,其中EMIFA支持64bit总线宽度。

2.3 信号生成模块

DDS信号产生模块采用三片ADI公司生产的AD9852ASQ,它们同时生成三路中频信号。根据雷达体制和信号处理机要求不同,可分别对应不同的信号,如雷达的目标回波、杂波和发射信号,或外辐射源雷达的直达波、目标回波和多径信号,以及跟踪雷达回波信号的和支路∑、俯仰左支路Δα以及方位差支路Δβ等。

AD9852最高工作频率300MHz,可工作在单频、FSK、Ramped FSK、Chirp、BPSK五种模式。具有丰富的寄存器组,通过设置相应控制字可方便生成多种信号。

2.3.1 总线及时序控制设计

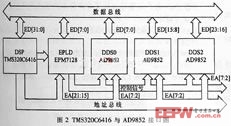

AD9852的频率、相位和幅度控制字的设置和控制信号的产生由TMS320C6416完成,AD9852可以看作是异步存储设备与TMS320C6416的EMIFA相连,EMIFA采用32bit总线。

AD9852采用并行输入,总线宽度为8位,数据传输速率可达100MHz。为了提高控制DDS的速度,本系统采用了地址总线复用、数据总线、“分裂”的技术。即三片AD9852的6位地址线同时占用TMS320C6416地址总线A2~A7位,而它们的数据线分别占用TMS320C6416数据总线的D0~D7、D8~D15和D16~D23位。这样可以由DSP对三片DDS的I/O缓冲寄存器同时进行写操作,提高了总线利用率,并保证了三片AD9852输出信号的相位相参。TMS320C6416与AD9852接口示意图如图2所示。

三片AD9852的控制时序信号由EPLD产生。本设计采用ALTERRA公司生产的可编程逻辑器件EPM7128AETC100,对TMS320C6416的高位地址信号、数据信号和控制信号编码,产生三片AD9852全局复位、读/写使能、频率或相位切换等控制信号。

写入AD9852的数据先存入I/O缓存器,在I/O更新信号到来时写入相应的寄存器改变AD9852的工作状态。本设计中,I/O更新信号既可以由DSP写完控制字后产生,也可由EPLD将系统时钟分频定时产生,两种方式的选择以及分频倍数的控制同样由EPLD对TMS320C6416的信号编码实现。

评论