达成最佳效能/成本的服务器ASIC IP与系统整合实现40nm高成本效益制造

弹性客制化IC设计领导厂商(Flexible ASIC Leader™)创意电子(Global Unichip Corp.,GUC)与高度创新的fabless Soc – centric IC芯片设计公司, 信骅科技(ASPEED Technology, Inc.)采用业界第一个以台积电公司40nm低功耗(Low Power,LP)工艺节点的DDR3/4 PHY,大幅加速了一远程管理控制器的系统设计, 此控制器用于服务器及桌面虚拟化。

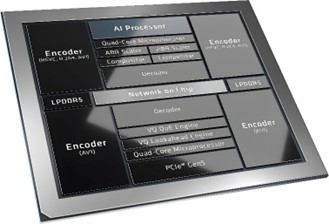

本文引用地址:http://www.eepw.com.cn/article/256843.htm创意电子的DDR 3/4 PHY为业界第一个以40nm低功耗制程技术制造,并提供低功耗、高效能与高成本效益的DDR 3/4 PHY IP。创意电子提供DDR3/4 PHY与controller完整解决方案,且在台积电最先进工艺,包括40nm LP、28nm HPM与16nm FF等工艺都有完整的布局。

在设计与生产过程中,双方公司的工程师们都面对了产品效能与上市时间的挑战。在设计端,ASPEED信骅科技的AST2500服务器SoC系列与AST3200桌面 虚拟化SoC必须在成本效益考虑下仍达成世界级的表现。

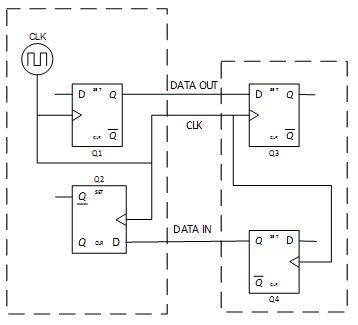

成功关键就在于透过精准的DDR系统仿真流程与测量校正,即使搭配精简的封装基板与PCB电路板, 仍能实现创意电子DDR3/4高速接口IP所能达到的最佳效能。

创意电子IGADDRS03A DDR3/4 PHY高速接口IP利用multiple oxide 内存I/O设计,达到DDR3与DDR4低功耗和高速运作的要求。此IP支持容易操作的PHY自动训练模式,能够缩短第一次系统开机时间并减少资源的耗用。IGADDRS03A能够与第三方IP和创意电子的DDR3/DDR4 controller轻松地整合。

ASPEED信骅科技总经理林鸿明表示:「创意电子的提供的IP、工艺节点与封装技术,克服了在40nm SoC上所遇到的成本效益的挑战。透过两家公司工程团队在这些领域的专业能力进而协同合作就是这个产品得以顺利量产的成功关键。」

创意电子总经理赖俊豪表示:「当今服务器芯片市场是高度竞争的。效能曾经是最重要的,但当今的服务器SoC必须在达成效能外仍符合成本效益。要达成ASPEED AST2500与AST3200成功量产这项佳绩, 需要真正创新的技术、业务创意、还有GUC与ASPEED的紧密合作,尤其在40nm制程上更是如此。」

评论