基于MSP430的高速线阵CCD采集系统设计

本文引用地址:http://www.eepw.com.cn/article/256596.htm

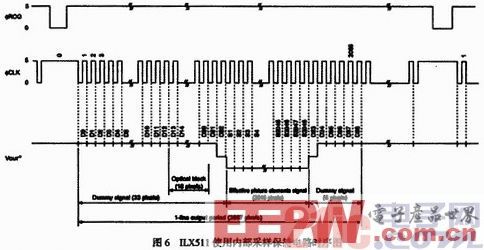

由图6可知,ILX511在完成初始化工作后,在每一个CLK时钟下降沿时输出信号。ILX511一个采样周期由2087个CLK周期组成,在前33个周期和最后6个周期输出无用信号(Dummy Signal),中间的2048个信号输出有用信号。因此,AD9220需要在CLK开始后第34个周期启动转换。AD 9220某次转换的结果在其输入后3周期输出,故FIFO需在AD9220第一次转换结果输出时启动写信号,即在CCD第37个CLK时启动。又由于CCD在CLK低电平时输出信号,AD9220在CLK高电平时采样和输出,FIFO写信号低电平时有效,故AD9220的时钟和CLK反相,FIFO写信号和CLK同相。

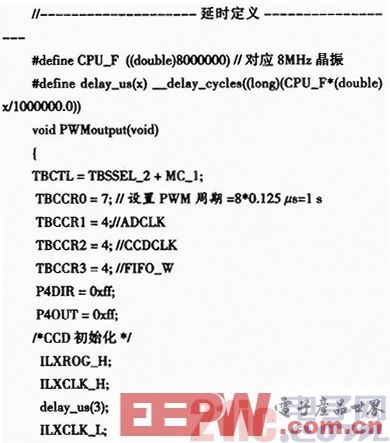

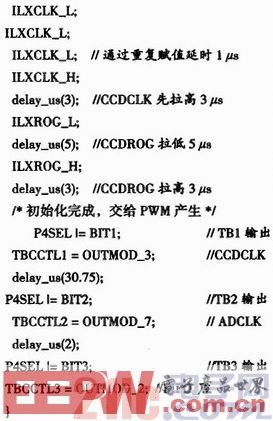

结合MSP430定时器灵活的PWM输出模式,CCD的CLK信号、AD9220的时钟和FIFO的写信号通过定时器B的引脚输出PWM信号实现,各个时钟周期之间的延时通过精准的延时函数实现。程序如下。

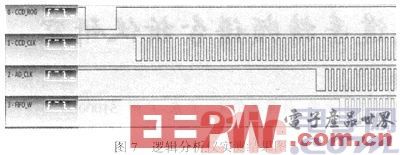

通过逻辑分析仪实测MSP430各引脚输出,结果如图7所示,各驱动信号时序正确,相位匹配良好,完全满足CCD及外围电路驱动时序要求。

3.3 通讯模块

通讯模块主要通过MSP430的中断完成发送数据到上位机的功能。通讯模块程序流程图如图8所示。

在ADC将CCD输出的数据全部转换完成并将FIFO存满后,IDT7203的FF标志位变低触发MSP430的外部中断服务程序。若需重新发送某次结果,需在进行下一次采集之前,由上位机发送“A”至下位机;若要继续采集,则由上位机发送“C”至下位机。MSP430产生串口接收中断后,判断是否进行重新发送、继续采集。

4 结束语

文中在分析线阵CCD器件驱动时序和外围电路特点的基础上,以MSP430作为主控芯片输出PWM的方式,创造性地提出了一种线阵CCD驱动电路和时序的设计方法。实验验证了所设计的系统能够很好地满足时序要求和实现整体功能。由于采用模块化设计,本系统可以和引脚兼容的同类CCD共用,同时可以结合MSP430低功耗特点作为模块组合应用在不同背景和需求中。

pwm相关文章:pwm是什么

模数转换器相关文章:模数转换器工作原理

评论