一款基于门控时钟的低功耗时序电路设计

电路运算

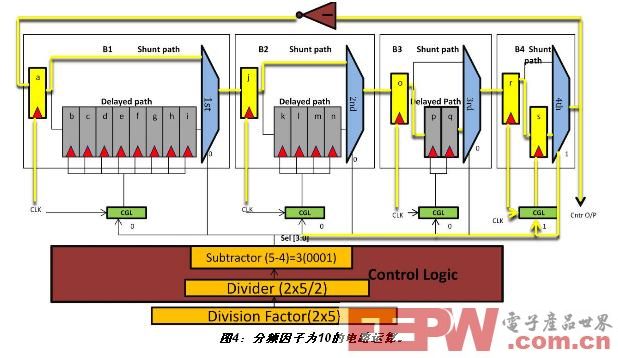

本文引用地址:http://www.eepw.com.cn/article/256541.htm以分频因子为10(即2N=10)的电路为例。由于传统约翰逊计数器在分频因子为2N时需要N个触发器,要使分频因子为10,电路中需要2N/2 = 10/2 = 5个触发器。分频器电路的输出是2N/2 = 5,这时减法器的输出则为(5-4) = 1,再馈入多路复用器的选择线路,其二进制表示为0001.这个4位sel[3:0]=0001信号极为重要,因为它不仅控制着门控时钟逻辑,还在分流和延迟路径中做出选择。

在这种情况下,只有Sel[0]会变为1并启用s触发器的时钟,并且同样地,sel[3]、sel[2]、sel[1]将相应禁用 (b、c、d、e、f、g、h、i)、(k, l, m, n)、(p、q)触发器的时钟,见图4中突显部分。另外需要注意的是,“a, j, o 和r”触发器将始终启用。这样一来,不仅启用了所需的触发器,并且该电路可在第4个多路复用器的输出上获得所需的输出时钟。因此,在这个示例中,共有5个触发器接收到时钟,其他触发器的时钟将自动被禁用。

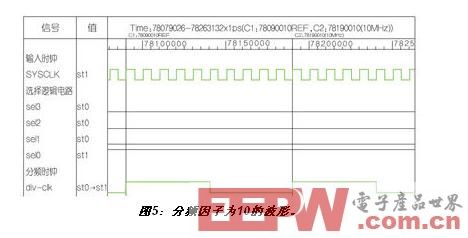

我们对上述计数器进行了模拟,其结果以RTL波形的形式呈现在图5中。根据图5可以推出:修改后的计数器采用sel[3:0]作为4'h0001,将一个100 MHz的时钟进行分频,提供10 MHz的输出。

推荐的电路可实现各种组合,表2列出了多路复用器所选择的输入。

推荐方法的优势

本文所介绍的约翰逊计数器可根据分频因子(范围为8至38)进行编程,按提供给计数器组合逻辑的输入所配置的提供一系列输出频率。

即使此计数器中配备了额外的硬件来实现可编程性,但是该电路的功耗通过一个逻辑提供的有效门控时钟进行控制,该逻辑与在选择阶段挑选多路复用器时所采用的逻辑相同,并启用门控时钟单元。

因此,将门控时钟添加到设计内以后,任何从移位寄存器传送至计数器的时序逻辑都可以变得更加高效,并且片上系统的一系列此类电路综合起来可以节省功耗并延长设备电池寿命。

总结

在设计阶段,由于架构师对电路的功耗要求越来越严格,并且倍增系数越来越大,因此对多路复用级联时钟分频器的需求也随之加大,但这种分频器会使电路消耗更多的功耗,并且占用更大的芯片面积。结构调整后的设计却提供了一个更加轻松的解决方案,与传统电路相比,重组后的电路可支持不同的输出频率,同时消耗更低的功耗。该解决方案还可轻松应用至各种其他设计中,使其他设计变得更加节能。

电路相关文章:电路分析基础

分频器相关文章:分频器原理 尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论