基于CPLD的异步ASI/SDI信号电复接光传输设备设计

引言

本文引用地址:http://www.eepw.com.cn/article/256486.htm近年来,随着计算机、数字网络和电视技术的飞速发展,人们对高质量电视图像的需求不断提高,我国广播电视事业日新月异、迅猛发展。四年前开通的数字电视卫星广播,目前已形成相当规模。数字摄录、数字特技、非线性编辑系统、虚拟演播室、数字转播车、网络硬盘阵列以及机械手数字播放系统等设备,已陆续进入中央电视台和各省市级电视台。标准高清晰度数字电视SDTV/HDTV已列为国家重大科研产业工程项目,试验播出已在中央广播电视塔上进行。目前,我国数字电视节目制作和数字电视地面广播已在紧锣密鼓地推进,而“十一五”将是我国数字电视整体平移的准备期,是广播电视系统从模拟向数字化过渡的重要阶段。

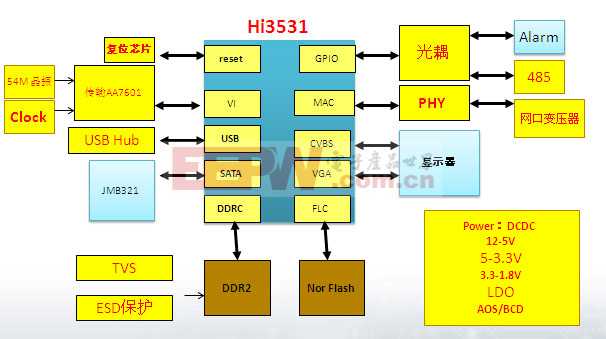

本设计正是为应对这一趋势,并为满足市场对于多路ASI/SDI数字视频信号光传输设备的巨大需求而设计的。它是通过时分复用技术实现在一根光纤中同时传输两路ASI/SDI数字视频信号的光传输设备,该项设计可为今后开发更多路更高速的异步数字信号光传输设备打好基础。

系统实现方案

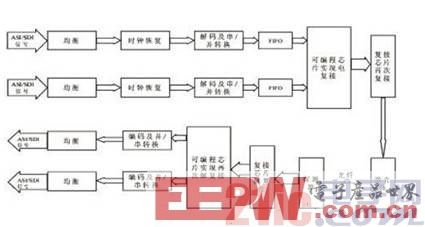

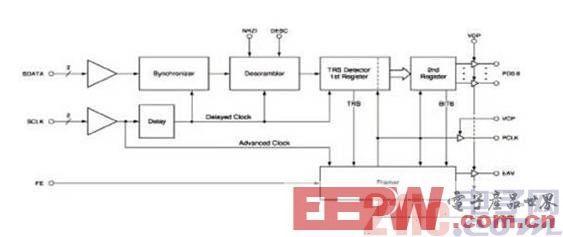

该ASI/SDI信号光传输设备的工作原理见图1。

图1 系统原理图

由图1可知,ASI/SDI串行信号通过均衡电路后得到整形,转变成为一组差分信号;再经过时钟恢复电路将信号中的时钟提取出来,以便在接下来的解码和同步信号时使用;再通过解码电路后,串行的高速信号转变成并行的低速信号,为接下来的电复接过程做好准备;最后通过FIFO电路的调整实现异步信号跟本地的电复接时钟同步,进而实现本地的电复接;再通过光模块电/光转换后传输到收端,收端收到信号后经过一系列逆向变换电路后,恢复出原始的ASI/SDI串行信号,完成整个传输过程。

本设计中ASI/SDI信号的电复接技术是整个技术环节的关键。由于项目中需电复接的ASI/SDI信号速率很高,标准速率达到270Mbit/s,并且不是同源的信号复接,所以直接对该信号电复接很困难且不经济,需要先恢复出各个信号的时钟,把高速串行信号变换成低速并行信号,然后再通过FIFO芯片电路来调整各个信号的时钟步伐,实现跟本地的时钟同步,然后再通过可编程芯片进行两路电信号复接,进而实现时分复用传输。只有经过这一系列的信号处理过程后,在接收端才可以实现顺利的解复接过程,这也是该设计的主要技术攻关点。

另外,电复接的锁定也是一个问题。信号路数越多,速率越高,越难锁定,对PCB板的排版技术要求较高。通过对各个元器件的合理放置和科学的滤除杂波等各项处理,这个问题可以得到很好的解决。

硬件电路

在该设计中,主要使用的是美国国家半导体公司最新推出的功能强大且性能稳定的数字视频芯片组。其中解码及串/并转换芯片选用CLC011;编码及并/串转换芯片选用CLC020;时钟恢复芯片选用LMH0046;自适应电缆均衡芯片选用CLC014;CPLD芯片采用LATTICE公司的 LC4256V;FIFO芯片采用IDT公司的IDT72V2105。

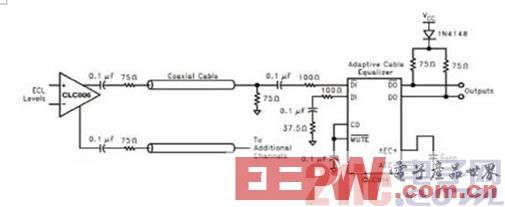

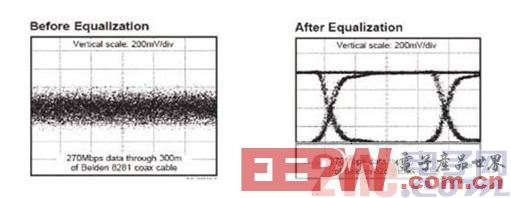

均衡部分电路处理过程如图2所示。由图2可知单端输入的ASI/SDI串行信号通过均衡电路后得到整形,转变成一组差分信号,为接下来的时钟恢复过程作好了准备。通过均衡电路以后,信号质量大大提高,输入输出信号波形比较如图3。

图2 均衡部分电路处理过程

图3 均衡电路波形比较

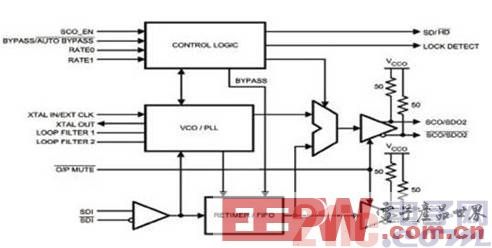

时钟恢复部分电路处理过程由图4所示。通过图4可以看到,正确地设置好芯片的工作模式,由本地提供一个27M的时钟供时钟恢复芯片使用,将均衡后的高速差分信号输入到芯片中,通过芯片处理后恢复出串行信号之中的时钟信号,以便下面解码部分电路使用。同时,该芯片也可支持高清信号的时钟恢复功能。

图4 时钟恢复部分电路处理过程

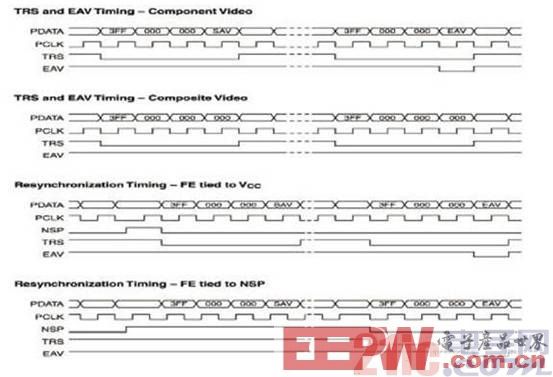

解码部分电路处理过程由图5所示。通过图5可以看到,由时钟恢复芯片恢复出来的串行时钟和串行数据输入到解码芯片,通过串/并转换后输出10位并行数据和27M的并行时钟,以备下面FIFO电路的时钟调整使用。具体各个工作模式下信号的时序图见图6。

图5 解码部分电路处理过程

图6 各模式信号时序图

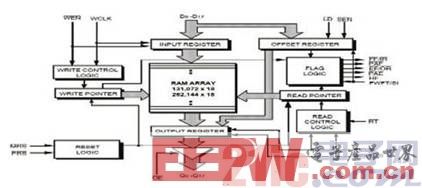

FIFO 部分电路处理过程如图7所示。其中读时钟使用编码电路恢复出来的27M并行时钟,写时钟使用本地的27M时钟,通过调整实现经过FIFO的10位并行信号与本地时钟同步,为接下来输入到CPLD进行电复接做好准备。CPLD的电复接部分程序如下,其中2BP-S为复接程序,2BS-P为解复接程序。

图7 FIFO部分电路处理过程

architecture SCHEMATIC of 2BP-S is

SIGNAL gnd : std_logic := '0';

SIGNAL vcc : std_logic := '1';

signal N_25 : std_logic;

signal N_12 : std_logic;

signal N_13 : std_logic;

signal N_15 : std_logic;

signal N_16 : std_logic;

signal N_17 : std_logic;

signal N_21 : std_logic;

signal N_22 : std_logic;

signal N_23 : std_logic;

评论