解析高速PCB设计中的时序分析及仿真策略

在网络通讯领域,ATM交换机、核心路由器、千兆以太网以及各种网关设备中,系统数据速率、时钟速率不断提高,相应处理器的工作频率也越来越高;数据、语音、图像的传输速度已经远远高于500Mbps,数百兆乃至数吉的背板也越来越普遍。数字系统速度的提高意味着信号的升降时间尽可能短,由数字信号频率和边沿速率提高而产生的一系列高速设计问题也变得越来越突出。当信号的互连延迟大于边沿信号翻转时间的20%时,板上的信号导线就会呈现出传输线效应,这样的设计就成为高速设计。高速问题的出现给硬件设计带来了更大的挑战,有许多从逻辑角度看来正确的设计,如果在实际PCB设计中处理不当就会导致整个设计失败,这种情形在日益追求高速的网络通信领域更加明显。专家预测,在未来的硬件电路设计开销方面,逻辑功能设计的开销将大为缩减,而与高速设计相关的开销将占总开销的80%甚至更多。高速问题已成为系统设计能否成功的重要因素之一。

本文引用地址:http://www.eepw.com.cn/article/256058.htm因高速问题产生的信号过冲、下冲、反射、振铃、串扰等将严重影响系统的正常时序,系统时序余量的减少迫使人们关注影响数字波形时序和质量的各种现象。由于速度的提高使时序变得苛刻时,无论事先对系统原理理解得多么透彻,任何忽略和简化都可能给系统带来严重的后果。在高速设计中,时序问题的影响更为关键,本文将专门讨论高速设计中的时序分析及其仿真策略。

1 公共时钟同步的时序分析及仿真

在高速数字电路中,数据的传输一般都通过时钟对数据信号进行有序的收发控制。芯片只能按规定的时序发送和接收数据,过长的信号延迟或信号延时匹配不当都可能导致信号时序的违背和功能混乱。在低速系统中,互连延迟和振铃等现象都可忽略不计,因为在这种低速系统中信号有足够的时间达到稳定状态。但在高速系统中,边沿速率加快、系统时钟速率上升,信号在器件之间的传输时间以及同步准备时间都缩短,传输线上的等效电容、电感也会对信号的数字转换产生延迟和畸变,再加上信号延时不匹配等因素,都会影响芯片的建立和保持时间,导致芯片无法正确收发数据、系统无法正常工作。

所谓公共时钟同步,是指在数据的传输过程中,总线上的驱动端和接收端共享同一个时钟源,在同一个时钟缓冲器(CLOCK BUFFER)发出同相时钟的作用下,完成数据的发送和接收。图1所示为一个典型的公共时钟同步数据收发工作示意图。图1中,晶振CRYSTAL产生输出信号CLK_IN到达时钟分配器CLOCK BUFFER,经CLOCK BUFFER分配缓冲后发出两路同相时钟,一路是CLKB,用于DRIVER的数据输出;另一路是CLKA,用于采样锁存由DRIVER发往RECEIVER的数据。时钟CLKB经Tflt_CLKB一段飞行时间(FLIGHT TIME)后到达DRIVER,DRIVER内部数据由CLKB锁存经过TCO_DATA时间后出现在DRIVER的输出端口上,输出的数据然后再经过一段飞行时间Tflt_DATA到达RECEIVER的输入端口;在RECEIVER的输入端口上,利用CLOCK BUFFER产生的另一个时钟CLKA(经过的延时就是CLKA时钟飞行时间,即Tflt_CLKA)采样锁存这批来自DRIVER的数据,从而完成COMMON CLOCK一个时钟周期的数据传送过程。

以上过程表明,到达RECEIVER的数据是利用时钟下一个周期的上升沿采样的,据此可得到数据传送所应满足的两个必要条件:①RECEIVER输入端的数据一般都有所要求的建立时间Tsetup,它表示数据有效必须先于时钟有效的最小时间值,数据信号到达输入端的时间应该足够早于时钟信号,由此可得出建立时间所满足的不等式;②为了成功地将数据锁存到器件内部,数据信号必须在接收芯片的输入端保持足够长时间有效以确保信号正确无误地被时钟采样锁存,这段时间称为保持时间,CLKA的延时必须小于数据的无效时间(INVALID),由此可得出保持时间所满足的不等式。

1.1 数据建立时间的时序分析

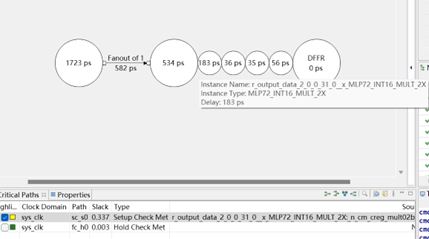

由第一个条件可知,数据信号必须先于时钟CLKA到达接收端,才能正确地锁存数据。在公共时钟总线中,第一个时钟周期的作用是将数据锁存到DRIVER的输出端,第二个时钟周期则将数据锁存到RECEIVER的内部,这意味着数据信号到达RECEIVER输入端的时间应该足够早于时钟信号CLKA。为了满足这一条件,必须确定时钟和数据信号到达RECEIVER的延时并保证满足接收端建立时间的要求,任何比需要的建立时间多出来的时间量即为建立时间时序余量Tmargin。在图1的时序图中,所有箭头线路表示数据信号和时钟信号在芯片内部或传输线上产生的延时,在下面的箭头线路表示从第一个时钟边沿有效至数据到达RECEIVER输入端的总延时,在上面的箭头线路表示接收时钟CLKA的总延时。从第一个时钟边沿有效至数据到达RECEIVER输入端的总延时为:

TDATA_DELAY=TCO_CLKB+Tflt_CLKB+TCO_DATA+Tflt_DATA

接收时钟CLKA下一个周期的总延时为:

TCLKA_DELAY=TCYCLE+TCO_CLKA+Tflt_CLKA

要满足数据的建立时间则必须有:

TCLKA_DELAY_MIN-TDATA_DELAY_MAX-Tsetup-Tmargin>0

展开并考虑时钟的抖动Tjitter等因素整理后得到:

TCYCLE+(TCO_CLKA_MIN-TCO_CLKB_MAX)+ (Tflt_CLKA_MIN-Tflt_CLKB_MAX)-TCO_DATA_MAX-Tflt_DATA_SETTLE_DELAY_MAX-Tjitter-Tsetup-Tmargin>0 (1)

式(1)中TCYCLE为时钟的一个时钟周期;第一个括号内是时钟芯片CLOCK BUFFER输出时钟CLKA、CLKB之间的最大相位差,即手册上称的output-output skew;第二个括号内则是CLOCK BUFFER芯片输出的两个时钟CLKA、CLKB分别到达RECEIVER和DRIVER的最大延时差。式(1)中TCO_DATA是指在一定的测试负载和测试条件下,从时钟触发开始到数据出现在输出端口并到达测试电压Vmeas(或VREF)阈值的时间间隔,TCO_DATA的大小与芯片内部逻辑延时、缓冲器OUTPUT BUFFER特性、输出负载情况都有直接关系,TCO可在芯片数据手册中查得。

由公式(1)可知,可调部分实际只有两项:Tflt_CLKB_MIN-Tflt_CLKB_MAX和Tflt_DATA_SETTLE_DELAY_MAX。单从满足建立时间而言,Tflt_CLKA_MIN应尽可能大,而Tflt_CLKB_MAX和Tflt_DATA_SETTLE_DELAY_MAX则要尽可能小。实质上,就是要求接收时钟来得晚一点,数据来得早一点。

1.2 数据保持时间的时序分析

为了成功地将数据锁存到器件内部,数据信号必须在接收芯片的输入端保持足够长时间有效以确保信号正确无误地被时钟采样锁存,这段时间称为保持时间。在公共时钟总线中,接收端缓冲器利用第二个时钟边沿锁存数据,同时在驱动端把下一个数据锁存到数据发送端。因此为了满足接收端保持时间,必须保证有效数据在下一个数据信号到达之前锁存到接收端触发器中,这就要求接收时钟CLKA的延时要小于接收数据信号的延时。

路由器相关文章:路由器工作原理

路由器相关文章:路由器工作原理

交换机相关文章:交换机工作原理

晶振相关文章:晶振原理

评论