研究天线电源故障检测电路的设计

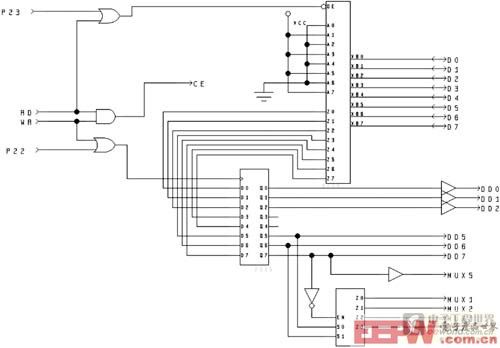

图6是CPLD内部逻辑电路,CPLD选用的是LATTICE公司的ispLSI1016E,逻辑设计采用原理图输入法,主要功能是对MUX的通道进行选择、对A/D转换器进行控制及产生自检代码等。图中有三个主要器件:数据双向开关、数据锁存器、译码器。数据双向开关的OE为低时,数据A0~A7传向单片机的数据线D0~D7,该数据正常时是自检代码AAH,当OE为高时,单片机数据传向CPLD内部的锁存器,用来对多路模拟开关进行选择。端口地址译码使用了单片机的RD、WR、P22、P23引脚,还使用了单片机的P20及P21引脚,它们分别连接到A/D转换器CS和CE端,具体地址定义如下:

CPLD自检测地址:0x0700

通道选择数据锁存器地址:0x0b00

A/D转换器写地址:0x0c00

A/D转换器读地址:0x0e00

信号MUX1~MUX5是MUX电路的前级芯片选择信号,高电平有效;DD0~DD2是MUX电路前级的通道选择信号,取值范围是0~34,对应模拟通道的1~35;DD5~DD7是MUX电路的后级通道选择信号,取值范围为0~4,分别对应前级的五个MUX的输出信号。这些信号的产生过程是:单片机通过数据线D0~D7将通道选择数据及芯片选择数据送到锁存器,产生通道选择信号DD0~DD2及DD5~DD7,再将部分数据进行译码产生MUX的片选信号MUX1~MUX5。

图6 CPLD逻辑电路

结语

目前该天线电源故障检测电路已经应用到某雷达中,随雷达系统通过设计定型,进入批量生产阶段,实践证明,该检测电路工作稳定可靠,能准确实时的对天线电源系统进行监测,故障检测率≥98%,故障隔离率≥95%,虚警率≤3%,达到设计要求。

评论