测试SDRAM控制器的PDMA

1引言

现代电子信息设备往往需要保存和处理大量的数字信息,一个高性能的Memory控制器可以大大提高系统的性能。在进行SDRAM控制器的设计时,需要考虑很多因素,设计完成以后还要进行多项测试看是否完全满足所要求的各项性能,为此我们设计了一个PDMA(Programmable Direct Mem o ry Access)用于测试SDRAM控制器的性能。在SoC中,SDRAM控制器往往跟多个IP模块(图形处理单元,音频处理单元等)交换数据,采用多个PDMA通道同时访问Memory可以真实模拟SDRAM控制器在SoC环境中被多个IP随机访问的情形。

2 PDMA的结构及工作原理

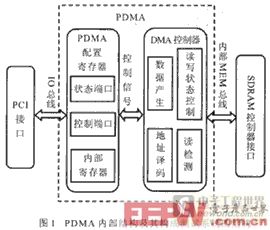

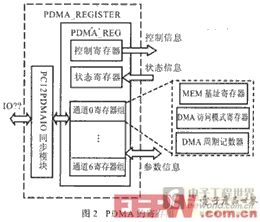

PDMA是可编程直接存储器存取的简称。图1 虚中框内是PDMA的内部模块结构,它主要由寄存器组和控制器两大部分构成,寄存器组用于保存配置参数和PDMA对SDRMA控制器访问后的状态信息及接收、启动、停止等控制信息。图2是 PDMA寄存器组的内部结构。

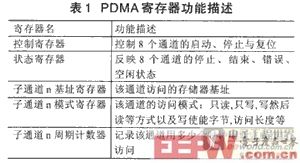

寄存器组模块里包含了一个同步模块、控制寄存器、状态寄存器和各通道的寄存器组。每一个子通道的寄存器组又包含访问基址寄存器、访问模式寄存器、周期计数器等三个寄存器。各寄存器的功能描述如表1所示。

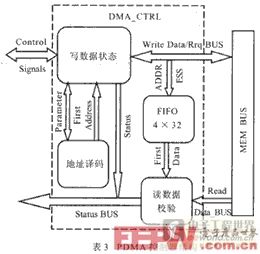

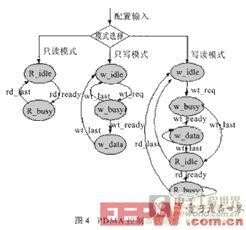

PDMA的控制器主要由:产生写数据的状态机、地址译码模块、FIFO以及读数据校验模块四部分构成。各PDMA控制器的结构如图3所示,其核心逻辑是一个状态机,我们采用一个两层嵌套的状态机来实现控制功能,如图4所示。

评论