探头在捕获高速信号上的技术进步

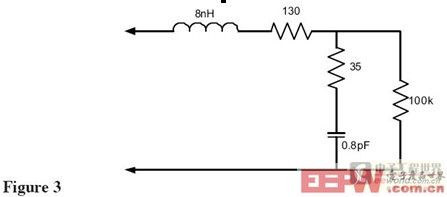

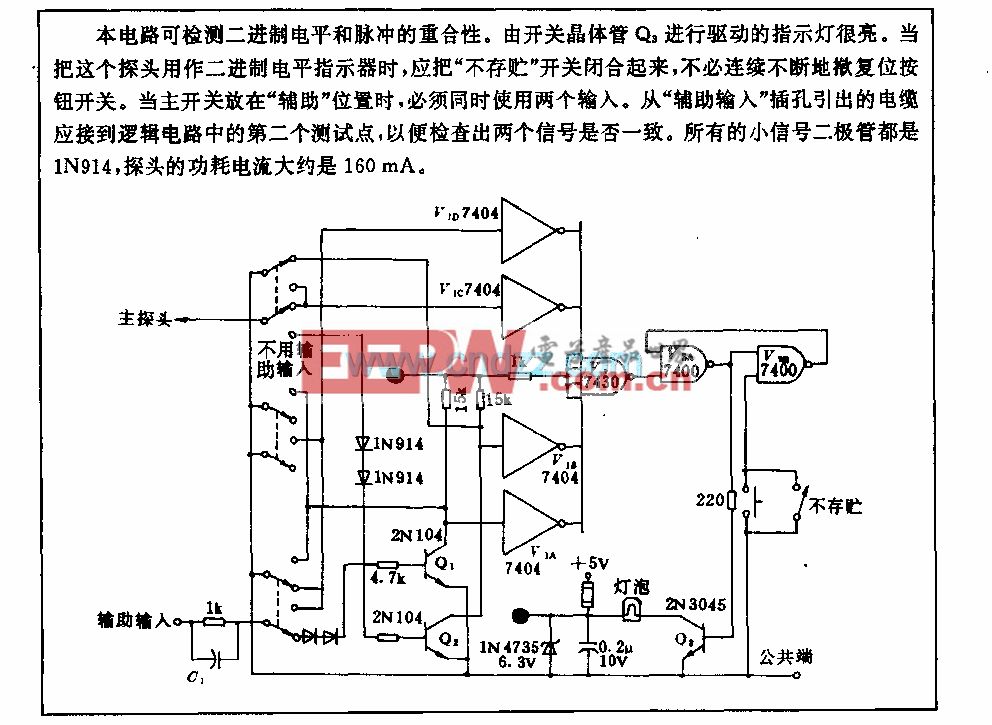

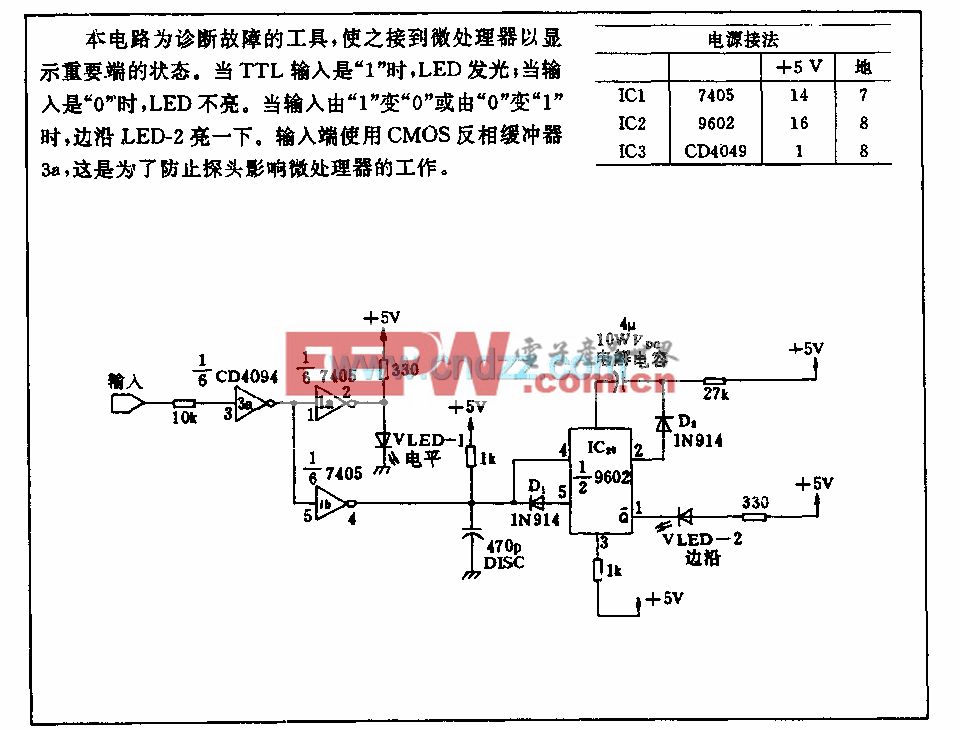

查看Figure 1中的等效电路,可以看到谐振频率(1/(2*PI*sqrt(LC))给出)点的探头输入阻抗是0欧姆——完全消除了被测信号!最近一些制造商开始注意这个问题并设计具有更好输入特性的探头。Figure 3展示了这种探头(Probe A)的等效电路。这是许多给出这个探头精确依赖于尖端和地夹的等效负载模型之一。这个探头还有一个谐振点大概是2GHz,该频点的阻抗被电阻限制到大约165欧姆。

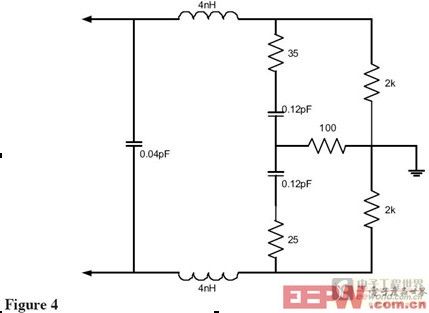

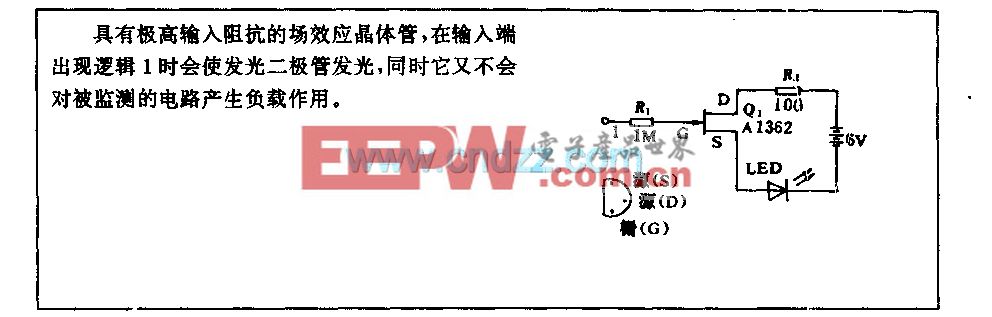

新的WaveLink差分探头的等效电路如Figure 4所示。设计包括抑制谐振阻抗的电阻,也能通过消除地夹电感减少电感。输入电容进一步减少到非常低的水平,有效的是谐振频率移到7GHz,好于单端探头。

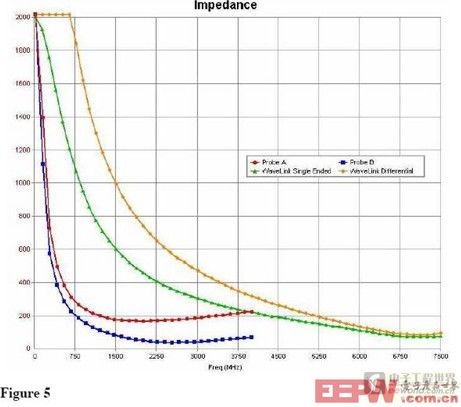

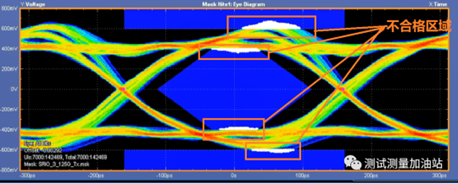

新设计的探头输入阻抗效应如何?Figure 5展示了Probe A阻抗 Vs 频率在有另外一个制造商没有仔细考虑减少输入谐振负载的Probe B之上。同时,新的WaveLink探头的负载效应也展示出来。由于是差分探头,有两条迹线——第一条显示了当做是单端探头(负输入当成是地连接)是时的阻抗,第二条显示了用平衡源驱动时的负载。迹线在每个探头的最大规定频率截止。

WaveLink和单端探头的一个明显区别是较低的DC电阻:4k 欧姆差分 vs 100k 欧姆。这是一个显著的不同,当检查阻抗 vs 频率曲线时,可以看到频率远大于几十MHz(事实上是这么一个探头所有关注的频率),8nH 130电抗器件占据了负载效应的主导。较低的输入电容提供了WaveLink探头一个较大的输入阻抗。

决定被测信号的阻抗效应并不简单,因为依赖于待测电路的阻抗。出于这个原因,阻抗 vs 频率曲线是不够的;精确的等效电路是首要的,因为特定待测电路的效应可以计算出来。

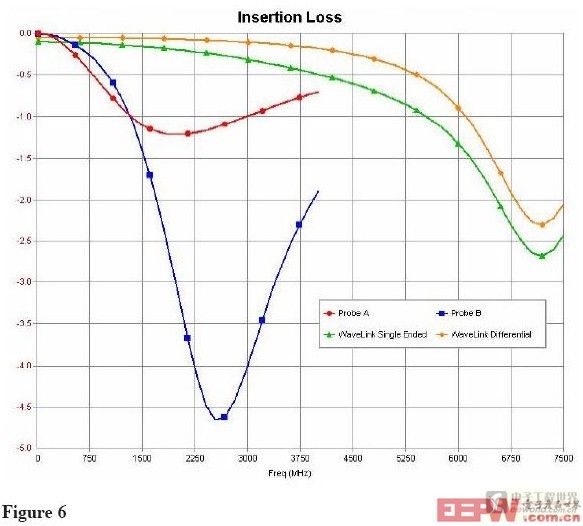

为了比较差分探头的性能,通常在良好定义和常数电路中画出负载效应。比如,每个探头在50欧姆理想环境中产生的插损如Figure 6所示。插损用dB表示;作为电压表示,必须除以20,采用反对数。比如Probe B导致的4.6dB的插损会产生41%的幅度损失。这对于被探测的信号有显著影响。

除了损失,待测电路的探头阻抗产生的时间误差。探头负载可对被测信号产生延迟,甚至比幅度损失更严重,因为这些通过系统传播。如果检测多个点,当探头放置到信号连接每个点产生一个时间偏移,这些延迟会增加。

评论