FPGA+DSP导引头信号处理中FPGA设计的关键技术

现代IC与FPGA设计巾使用的综合工具可以保证设计能满足每个数字电路触发器对建立与保持时间的要求。然而,异步信号却给软件提出了难题。对新的时钟域米说.从其它时钟域传柬的信号是异步的。大多数综合丁具在判定算步信号是否满足触发器时序要求时遇到了麻烦。因为它们不能确定触发器处于非稳态的时间,所以它们也就不能确定从一个触发器通过组合逻辑到达下一个触发器的总延迟时间。所以,最好的办法是使用一些电路来减轻异步信号的影响。

同步措施归纳起来主要有两方面,

1)对于跨越时钟域控制信号,用同步器来实现同步;

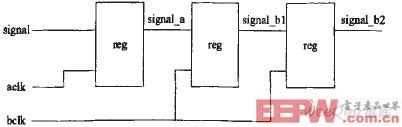

为了使同步。工作能正常进行,从某个时钟域传来的信号应先通过原时钟域上的一个触发器,然后不经过两个时钟域间的任何组合逻辑,直接进入同步器的第一个触发器中(图3)。这一要求非常重要,因为同步器的第一级触发器对组合逻辑所产生的毛刺非常敏感。如果一个足够长的信号毛刺正好满足建立一保持时问的要求,则同步器的第一级触发器会将其放行,给新时钟域的后续逻辑送出一个虚假的信号。

图3同步器示意

一个经同步后的信号在两个时钟沿以后就成为新时钟域中的有效信号。信号的延迟是新时钟域中的一到两个时钟周期。一种粗略的估算方法是同步器电路在新时钟域中造成两个时钟周期的延迟,设计者需要考虑同步延迟将对跨时钟域的信号时序造成的影响。

2)对于跨越时钟域的数据总线,要通过FIFO或RAM达到同步的目的。

数据在时钟域之间的传递是多个随机变化的控制信号在时钟域之间传递的一种实例。这种情况下,用同步器米处理同步问题往往不能收到满意的效果,因为多位数据的变化将会使同步器的采样错误率大大增加。常用的数据同步方法有两种:一种是用握手信号;另一种是用FIFO,一个时钟存数据。另一个时钟取数据。

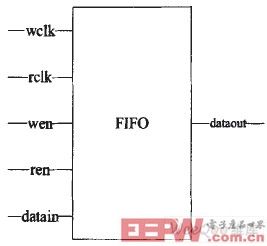

时钟域之间的数据传输用得最多的是FIFO,采用Xilinx自带的FIFO核来实现比较简单方便,图4足Xilinx提供的FIFO核的一个简单的示意图.wclk为写时钟,rclk为读时钟,FIFO深度通过读写使能wen和ren控制。

图4 FIFO核示意图

3.2、FPGA与DSP数据交互

实际应用过程中,DSP和FPGA程序设计往往是由不同的设计人员分工完成,在最后系统联调时,这两者之间的数据传输经常占用大量的调试时间,成为约束工程进度的关键凶素。因此,DSP与FPGA间接口和传输方式的选择与设计,是系统设计中必须要考惑的问题。

评论