基于uSB 2.0接口的高速数据采集系统设计

LJSB(Universal Serial Bus),其中文名称为"通用串行总线"。他是为了解决计算机外设种类口益增加与有限的主板插槽和端r丁之间的矛盾.由Intel,Microsoft,IBM,NEC,lucent等7家厂商共同制定的总线标准。目前,常用的LISB 2.O版本支持的最高传输速度可达到480 Mb/s.他以速度快、成本低、可靠性高、支持即插即用和热插拔等优点,迅速得到众多PC厂商的大力支持。同时,开发这种基于uSB 2.0的高速数据采集系统,代表了现代数据采集和传输系统的发展趋势,他也将被越来越多的用户所接受。

l 系统硬件整体设计

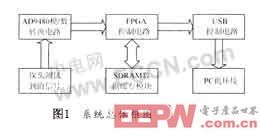

该系统总体框架为PC机(能支持USB 2.O协议的计算机)、A/D转换模块、FPGA控制模块、LYSB控制模块,如图l所示。

从整体上看结构可分为2个部分:高速数据采集模块的设计;USB 2.O高速数据传输系统。

1.1数据采集模块

该系统主要由l片高速AD 芯片、1片SDRAM和l片A1tera公司的FPGA构成。由于系统设计采样速度最大为1()0 MHz.据采样定理,采样频率至少应在200MHz以上,所以A/D芯片采用Analog公司的高速A/D芯片AD9480。该芯片转换精度8 b.单一3.3 V电源供电,低功耗,最高工作速度为250 MS/s,采用差分形式、LVDS电平输出,经过测试可以很好地满足系统要求。

为了满足数据采集中高速实时流数据的应用,避免FIFO溢出,本系统通过FPGA及SDRAM构造一个大容量的FIFO,可以提供一个低成本并且能满足高速实时流数据传输的方案。

低速数据采集系统常使用MCU作为CPU来控制,但在高速数据采集系统中,采样速度往往受MCU速度的影响,而且随着速度的提高,ADC,SDRAM和MCtJ之间的时序同步问题也显示出来,因此系统使用了高速FPGA芯片来控制ADC和SDRAM,从而很好地解决了时序精度和同步的问题。

FPGA选择A1tera公司的CYCLONE系列高性价比产品EPlC6T144C8。他基于1.5 V,O.3 μm及全层铜SRAM工艺,其密度增加至20 060个逻辑元件(LE),RAM增加至288 kb。他具有锁相环以及DDR SDR和速度周期RAM(FCRAM)存储器所需的专用双数据(DDR)接口等。CYCLONE器件支持多种I/O口标准,包括640 Mb/s的LVDS,以及速率为33 MHz和66 MHz,数据宽度为32 b和64 b的PCI。FPGA实现的功能逻辑主要有:实现对ADC的控制,开始A/D转换;为ADC同步提供SDRAM地址计数和写信号,把每次A/D转换的结果直接存入SDRAM,并自动增加地址;当地址计数器达到最大时,发出RAMFULL中断信号,提示SDRAM已满。

FPGA的功能逻辑用VHDL语言实现,其编译和仿真使用Altera公司的QuartusⅡ5.1,使用ByteBlastⅡ并行编程电缆和JTAG口下载编程和配置文件。

1.2 USB 2.0高速数据传输

用于USB设备开发的芯片通常有2种类型:一种是MCU集成在芯片里面,如CYPRESS的EZ-USB;另一种是纯粹的USB接口芯片,仅处理USB通信,使用时必须由外部微控制器(MCU)进行控制,如Philips的PDIUSBD1 2,National Semiconductor的USBN9604等。在本设计中经过论证分析,采用第一种类型,采用Cypress公司的EZ-USB FX2系列的CY7C68013芯片。

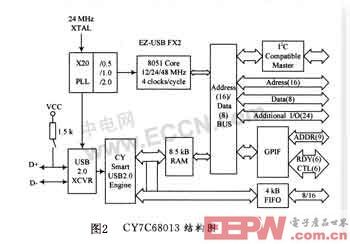

1.2.1 EZ-USB FX2(CY7C68013)芯片

Cypress公司的EZ-USB FX2系列芯片是最早符合USB 2.0协议的微控制器之一,他集成了符合USB 2.O协议的收发器(transceiver),串行接口引擎(SIE),增强型的8051内核以及可编程的外围接口。FX2系列芯片独特的结构使得数据传输速度最高可达56 Mb/s,最大限度地满足了USB 2.O的带宽。CY7C68013集成标准8051内核,且具有下列增强特性:可以达到48 MHz时钟;每条指令占4个时钟周期;2个USARTS;3个定时/计数器;扩展的中断系统;2个数据指针。

805l程序从内部RAM开始运行,借助如下3种方式进行程序装载:通过USB下载,从E2PROM中装载;通过外部存储器设备。内部集成了达4 kB的FIFO,用户程序发送数据时,直接从FIFO里读取,保证了数据高速传输,与外部实现透明数据传输。

1.2.2 硬件连接

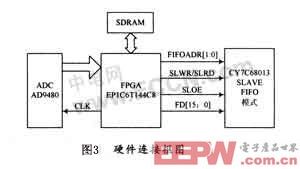

根据系统对数据传输的速度和实时性的要求,配置CY7C68013工作的接口模式为Slave FIFO模式。当进行数据采集时,硬件连接方式如图3所示。

A/D转换器的采样时钟同时作为CY7C68013的Slave F=IFO模式的读写控制时钟,即CY7C68013的接口时钟连接到IFCLK引脚。SLWR/SLRD是CY7C68013Slave FIFO的写使能/读允许信号。FPGA向CY7C268013Slave FIFO提供Slave FIFO输出允许信号SLOE,仅在数据输出时有效。FD[15:0]为16 b双向数据总线。FI-FOADR[1:0]为端点FIFO选择信号。在数据输入时固定为OO,选择端点2;在数据输出时固定为10,选择端点6。

2 系统程序设计

USB系统的软件设计可分为3部分:固件设计、驱动程序设计和用户端的应用程序设计。

2.1 固件(firmware)设计

固件程序实际上就是单片机方面的软件设计,他是所有基于微控制器及其外围电路的功能设备正常工作必不可少的部分,其作用就是辅助硬件。

评论