LTE标准下Turbo码编译码器的集成设计

为节省硬件资源,本文设计的Turbo码译码器采用子译码器单核复用的结构模式。当子译码器模块作为子译码器1时,信息比特顺序写入存储器后顺序读出到子译码器中,L_a2以交织地址写入存储器,顺序地址读出作为子译码器1的先验信息,同时校验位选择yp1,子译码器1根据3个输入进行SISO(软输入软输出)译码运算,得到新的L_a2及L_e;此后子译码器作为子译码器2,以交织地址将ys从存储器中读出,L_a2以顺序地址写入存储器,交织地址读出作为子译码器2的先验信息,同时校验位选择yp2,子译码器2根据3个输入进行SISO(软输入软输出)译码运算,得到新的L_a2及L_e,完成一次迭代。在满足迭代停止准则以后,将L_e解交织后进行硬判决,得到译码序列。

设计中,子译码器采用复杂度与性能折中的Max-Log-MAP译码算法。根据输入的信息位、校验位及先验概率信息,在时序控制模块的管理下,分别进行分支转移度量、前向状态度量、后向状态度量和对数似然比的计算及存储,以备下次译码运算调用。

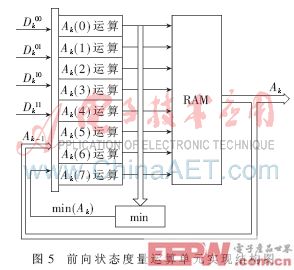

依据初始化分支转移度量值,由(13,15)RSC的篱笆图,找出当前时刻前向状态度量与前一时刻前向状态度量的对应关系[7],计算当前时刻的前向状态度量。依次递推,为防止数据溢出范围,每次迭代对其进行归一化处理,得到实现框图如图5所示。后向状态度量与前向状态度量具有相似的运算结构,只是逆向递推而已。

由对数似然比的定义,将得到的分支转移度量、前向状态度量和后向状态度量代入运算公式[8],对3种输入参量进行组合运算,然后取出“1”路径8种状态中的最小值和“0”路径8种状态的最小值,做差即得到Max-Log-MAP算法中的对数似然比。迭代数次后进行辅助硬判决,解交织输出即为传回信宿的译码序列。

3 系统实现与仿真结果分析

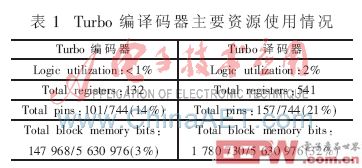

在Quartus Ⅱ开发工具上,以Stratix III 系列的EP3-SL150F1152C2为配置平台,用Verilog HDL语言对上述各功能模块进行编程建模,调试统一后编译综合,得到编译码器主要硬件资源占用情况如表1所示。

建立波形文件,分别对Turbo码进行时序仿真,得到信息帧长分别配置为128、512时,Turbo码编码器的仿真波形如图6(a)、图6(b)所示。''

图6中,每帧码字序列的结尾,都有12个系统尾比特,以使编码器寄存器回归全零状态。经多次验证,与Matlab仿真数据进行对比,结果正确。

将编码码字量化后存储于ROM中,提供给译码器进行时序仿真,得到信息帧长分别配置为128、512(码字序列长度分别为396、1 548)时,Turbo码译码器的仿真波形如图7(a)、图7(b)所示。

图7中,译码器首先根据帧长设置初始化交织图样,然后对系统码字解复接,得到信息序列(ys)、校验位1(yp1)及校验位2(yp2),与外信息(L_all)一起输入子译码器进行SISO译码运算,迭代6次以后判决得到译码结果(decoderout)。

设置不同的信息帧长,经多次仿真验证,均能正确实现编译码功能。将程序下载配置到EP3SL150F1152C2中,利用VC软件编写测试窗口,进行测试。结果显示,本设计可以利用外围键盘电路自行输入帧长,进行交织运算,得到交织图样,并能正确实现Turbo编译码功能,达到了设计要求。

本设计以LTE为应用背景,实现了一种可根据信道环境现场配置帧长的Turbo编译码的硬件方案。将QPP交织算法集成于FPGA内部,充分利用其时钟频率高、速度快的优势,减小了外围接口电路消耗。在系统初始化时进行交织运算,先于Turbo编译码进程开始,两者分时工作,协调统一,不会带来额外的时延。所实现的Turbo码编译码器是一种比较理想的通用型方案,为LTE标准下Turbo编解码专用集成芯片的开发与推广提供了参考。

评论