基于CPCI接口的SpaceWire总线通讯模块设计

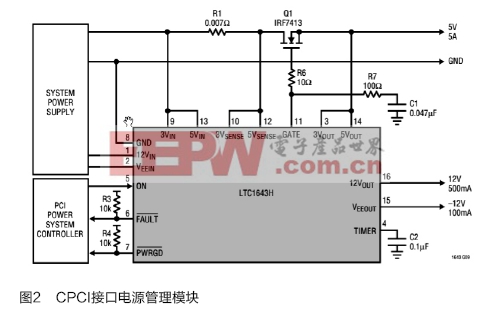

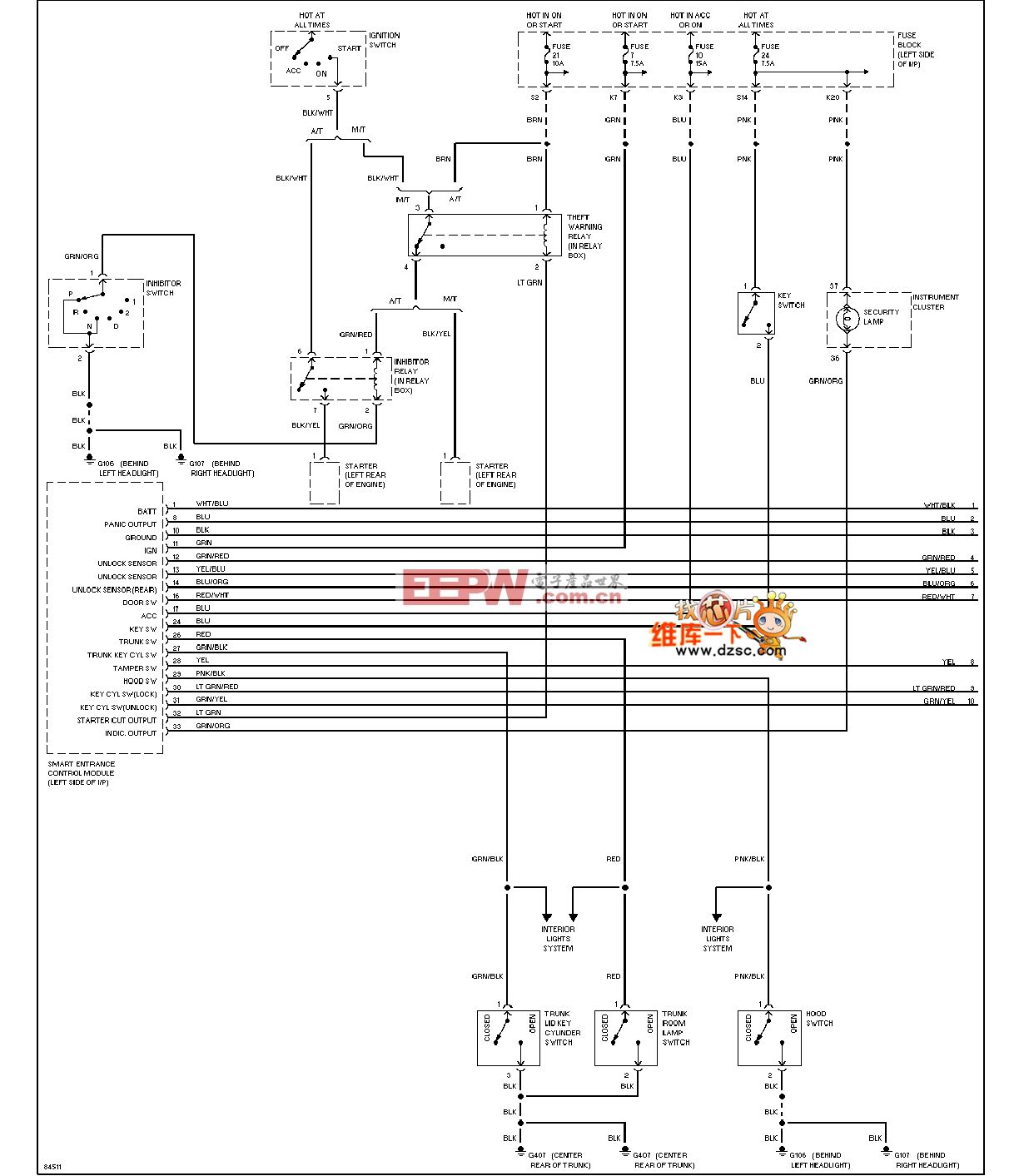

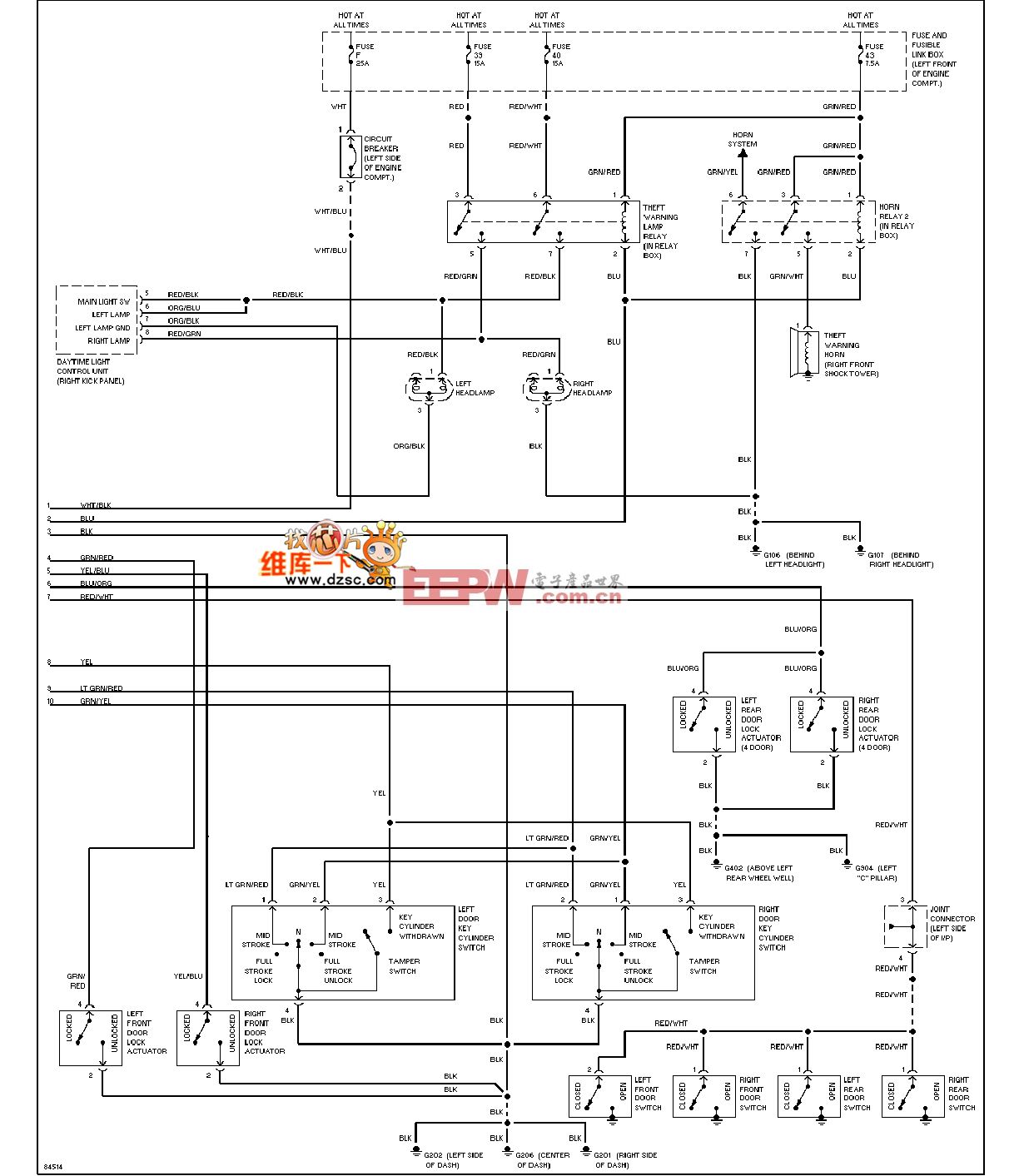

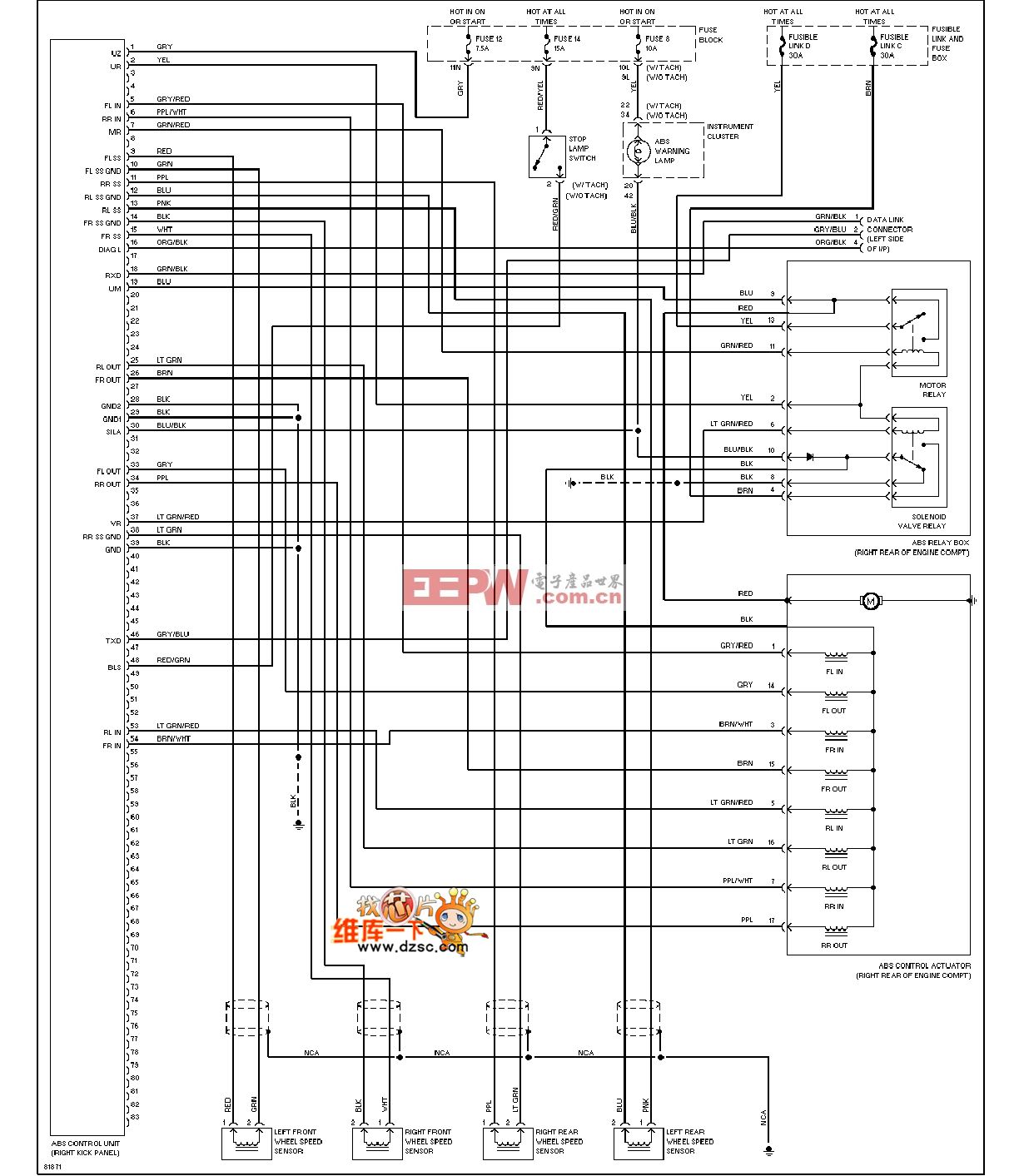

PCI9056的引脚BD_SEL#是CPCI接口中最小的插针之一,BD_SEL#连接LTC1643L的使能引脚,低电平时有效开启LTC1643L工作并同时给板卡供电。R10是一个0.018欧姆,0.5W,精度为1%的精密电阻,用于过流保护的电压检测电阻。当板卡发生故障导致电流超过额定值之后,R10两端的压差将增大,SENSE引脚将此过流信息反馈至LTC1643L电源管理器,同时切断电源供应,起到电源过流保护的功能。

本文引用地址:http://www.eepw.com.cn/article/247468.htm4 PCI桥接电路分析

在SpaceWire总线节点终端系统与航电计算机系统之间实现PCI通讯大致有两个方式,其一就是采用可编程器件作为一个独立的模块实现PCI协议,另一种方式就是采用专用PCI协议芯片。本系统的设计出于性能稳定性和结构简易性方面的考虑,选择用PLX公司生产的PCI9056集成芯片,该芯片可以设置成多种传输模式,完成SpaceWire总线节点与航电设备之间的通信桥接功能。

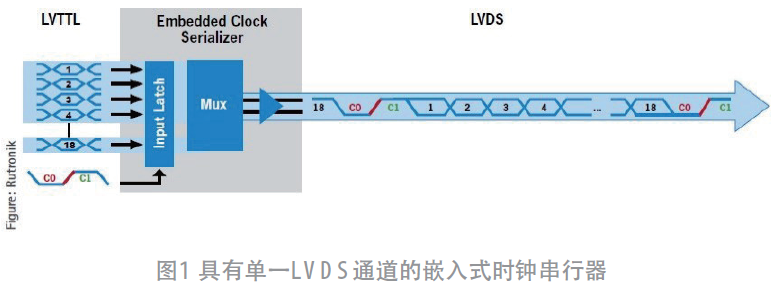

在PCI9056与本地FPGA之间的通信分为直接主模式(Direct Master Mode)、直接从模式(Direct Slave Mode)和DMA模式。由于PCI通信要求达到SpaceWire总线网络的2Mbit/s至400Mbit/s通讯速率(本板卡实现了200Mbit/s),这里采用的芯片时钟频率为66MHz,传输模式为直接从模式,工作时序如图3所示,PCI9056为主芯片,FPGA为从芯片。

为了与PCI9056进行高效的数据通信,FPGA内部划出了一部分内存以配置成双口RAM的形式完成PCI9056对SpaceWire数据的收发以及相应控制寄存器的控制传输。

5 Windriver软件的驱动生产

通过PLXMON软件对PCI9056的配置芯片进行配置后,可以利用Windows操作系统中WinDriver自动生成PCI驱动程序,步骤如下:首先启动WinDriver Wizard,从开始菜单,选择“程序 | WinDriver | Driver Wizard”;然后在Driver Wizard 菜单, 单击“File New Project”菜单来新建一个工程,从即插即用列表中选择显示卡,通过生产商的名字来选定。单击“Memory”标签。该显示卡的三个内存范围显示出来。内存范围中的BAR2映射的是FPGA内的RAM缓存块和专用寄存器,根据FPGA内核对这些缓存块和寄存器的可读写定义,可以在BAR2映射的区域里进行读写,若写进去的数值跟读出来的数值一致,表面CPCI接口通信正常。最后一步为生成驱动代码:单击“Build | Generate code”菜单, Driver Wizard 将产生操作硬件资源的函数,可以在用户模式下在应用程序中直接使用这些函数,这个向导还会产生一个样本程序来使用这些函数操作硬件,上层界面的开发可以直接调用这些API函数。

6 总结

本文是珠海欧比特公司为面向我国航天应用研发的一款SpaceWire总线节点终端板卡的一个实际应用设计方案,并根据此方案完成了对每个功能模块的结构和功能分析,欧比特公司此已经对方案设计申请了专利保护。此方案对今后SpaceWire总线在其它任务中的应用具有重要的借鉴意义。

dc相关文章:dc是什么

数字通信相关文章:数字通信原理

通信相关文章:通信原理

评论