基于FPGA的高速数传中定时同步设计

5 算法实现

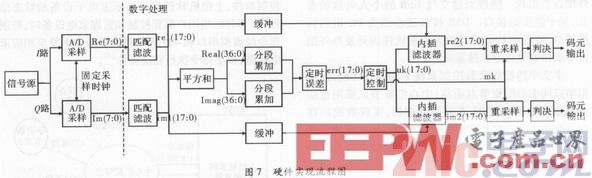

本文引用地址:http://www.eepw.com.cn/article/246961.htm在Matlab仿真性能得到保证的前提下,文中对该算法进行了硬件实现,并取得了良好的效果。算法硬件实现流程,如图7所示。

信号源部分使用信号发生器产生300 MHz的BPSK信号,A/D采样率为1.2 GHz,A/D直接对基带信号以4倍的符号率采样,匹配滤波的滚降系数为0.5,数字处理部分采用Xilinx公司的Virtex-4系列FPGA芯片。算法实现消耗8%的Slices以及14%的DSP48s。

使用Chipscope观察,当信噪比为15 dB时,定时同步前后的星座图对比如图8所示。

6 结束语

设计了基于数字滤波平方的全数字接收机定时同步方法,定时同步环路主要由定时误差提取、定时控制与内插滤波器3部分组成。其中定时误差是由基带采样信号进行离散傅里叶变换提取得到,并且文中设计了一种适用于高速通信下的并行实现结构,内插系数由定时控制模块计算的小数间隔确定,从定时控制模块计算出的整数间隔相当于重采样时钟,对内插后的信号进行采样,即可得到同步数据。数字滤波平方法属于非数据辅助型,对载波不敏感,可以先于载波同步进行,算法实现结构属于前馈式,适合于突发通信、运算简单、系统实现方便,Matlab仿真与硬件实现结果表明,该设计方案可以较好地解决定时问题。

fpga相关文章:fpga是什么

数字滤波器相关文章:数字滤波器原理

评论