基于TMS320C6202的装甲战车智能图像跟踪系统硬件平台设计

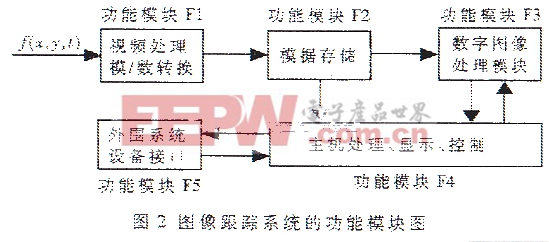

1 系统功能分析 本文设计的智能车载图像跟踪系统以DSP作为核心处理器,系统构成如图1所示。它首先利用欠采样技术进行全视场搜索以发现目标或人为指定目标,系统接收到跟踪指令和目标某一点的坐标参数(x0,y0)后,自适应地在目标指定位置附近开处理窗;然后利用给出的各种算法对处理窗内的图像数据进行处理,计算出目标准确地位置参数。在后续帧的处理中,处理窗的位置由上一帧求得的目标位置确定,逐帧处理就可以完成对目标的跟踪任务。这样,系统既能快速进行全视场的搜索,又能减小计算量,提高速度。 为实现上述基本功能,可将系统功能划分为几个基本功能模块,如图2所示。图3(1) 视频处理模/数转换模块(F1)。它包括视频信号的预处理、A/D转换,即把输入的信号转换成系统能够处理的数字图像数据。 (2) 数据存储模块(F2)。将A/D转换出来的数字图像数据按照一定的组织形式放在确定的存储区域。 (3) 数据图像处理模块(F3)。运用相关的数字图像处理算法实现目标的识别与跟踪,该模块是图像跟踪系统的核心。 (4) 主机模块(F4)。PC104嵌入式计算机在系统中的作用是负责协调各个模块的工作:显示图像及跟踪结果、执行DSP程序加载控制。 (5) 外围接口模块(F5)。与系统其它设备进行通信,包括接收用户输入、伺服机构控制等。

1 系统功能分析 本文设计的智能车载图像跟踪系统以DSP作为核心处理器,系统构成如图1所示。它首先利用欠采样技术进行全视场搜索以发现目标或人为指定目标,系统接收到跟踪指令和目标某一点的坐标参数(x0,y0)后,自适应地在目标指定位置附近开处理窗;然后利用给出的各种算法对处理窗内的图像数据进行处理,计算出目标准确地位置参数。在后续帧的处理中,处理窗的位置由上一帧求得的目标位置确定,逐帧处理就可以完成对目标的跟踪任务。这样,系统既能快速进行全视场的搜索,又能减小计算量,提高速度。 为实现上述基本功能,可将系统功能划分为几个基本功能模块,如图2所示。图3(1) 视频处理模/数转换模块(F1)。它包括视频信号的预处理、A/D转换,即把输入的信号转换成系统能够处理的数字图像数据。 (2) 数据存储模块(F2)。将A/D转换出来的数字图像数据按照一定的组织形式放在确定的存储区域。 (3) 数据图像处理模块(F3)。运用相关的数字图像处理算法实现目标的识别与跟踪,该模块是图像跟踪系统的核心。 (4) 主机模块(F4)。PC104嵌入式计算机在系统中的作用是负责协调各个模块的工作:显示图像及跟踪结果、执行DSP程序加载控制。 (5) 外围接口模块(F5)。与系统其它设备进行通信,包括接收用户输入、伺服机构控制等。 2 系统硬件设计 下面详细介绍系统硬件的总体方案及关键部分的设计。 这里提出了一个以TI公司的TMS320C6202高速DSP为核心并配以嵌入式PC104计算机系统的双CPU主从式实时跟踪系统,其硬件结构如图3所示。 结合图2和图3可以看出:功能模块F1由硬件单地FS1完成;功能模块F2由硬件单元FS2完成;功能模块F3由硬件单元FS3完成;功能模块F4由硬件单元FS4和FS5完成;功能模块F5由硬件单元FS5完成;硬件单元FS6完成系统的总线仲裁和逻辑控制功能。 视频A/D转换芯片选取的是PHLIPS公司的SAA7111A,这是一款增强型的视频输入片器,包含两个通道的模块预处理电路。系统的总线仲裁和逻辑控制电路采用Xilinx公司的大规模FPGA—XCV50E实现。通过一片大容量的FPGA实现对所有器件如输入缓冲FIFO、SRAM、DSP、FLASH编程、PCI接口电路等的逻辑控制。利用FPGA芯片的在系统内可编程(ISP)性能,可以使系统硬件的调试变得非常方便。

2 系统硬件设计 下面详细介绍系统硬件的总体方案及关键部分的设计。 这里提出了一个以TI公司的TMS320C6202高速DSP为核心并配以嵌入式PC104计算机系统的双CPU主从式实时跟踪系统,其硬件结构如图3所示。 结合图2和图3可以看出:功能模块F1由硬件单地FS1完成;功能模块F2由硬件单元FS2完成;功能模块F3由硬件单元FS3完成;功能模块F4由硬件单元FS4和FS5完成;功能模块F5由硬件单元FS5完成;硬件单元FS6完成系统的总线仲裁和逻辑控制功能。 视频A/D转换芯片选取的是PHLIPS公司的SAA7111A,这是一款增强型的视频输入片器,包含两个通道的模块预处理电路。系统的总线仲裁和逻辑控制电路采用Xilinx公司的大规模FPGA—XCV50E实现。通过一片大容量的FPGA实现对所有器件如输入缓冲FIFO、SRAM、DSP、FLASH编程、PCI接口电路等的逻辑控制。利用FPGA芯片的在系统内可编程(ISP)性能,可以使系统硬件的调试变得非常方便。 2.2 总线仲裁与逻辑控制设计 以DSP+PLD方式设计的电子系统充分发挥了DSP在数字信号处理方面的优势和可编程器件在控制逻辑方面的灵活性。 2.2.1 系统总线仲裁方案 系统中的数据交换是由总线来实现的,因此总线的管理是一个极为重要的问题。只有恰当地把总线分配给相应的总线使用设备,系统才能稳定高效地工作。特别是在一条总线上挂接多个设备,并且它们都需要占用总线(即它们都能成为这条总线的主设备)的时候,就产生了总线的竞争问题。这时候可以通过总线仲裁来解决总线的竞争问题。通过总线仲裁,可以实现多个设备以分时共享的方式占用一条总线。在总线的仲裁方案中,常常会指定一个总线的缺省占有设备。总线的缺省占有设备是指缺省状态的总线占用者,其它设备需要使用总线的时候,可以通过总线仲裁器向该设备申请总线的使用权,使用完以后再把总线释放出来。 图4是TMS320C6202的EMIF总线挂接的外设的示意图。从图中可以看出,EMIF接口总线上挂接了以下几个设备:DSP、SRAM、FLASH、逻辑控制电路,其中DSP和逻辑控制电路可以成为EMIF接口总线的主设备。DSP复位后,默认的状态是总线的从设备,当它需要成为总线的主设备的时候,就得向外部总线仲裁器(FPGA)申请总线。主计算机需要读取图像数据时,先给FPGA发送请求,然后FPGA收回EMIF的部线控制权,PCI9054通过FPGA读取SRAM中的图像数据。图5是系统进入 正常跟踪状态时EMIF总线的占用时序图。

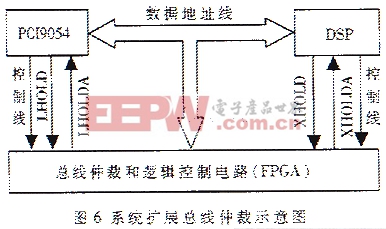

2.2 总线仲裁与逻辑控制设计 以DSP+PLD方式设计的电子系统充分发挥了DSP在数字信号处理方面的优势和可编程器件在控制逻辑方面的灵活性。 2.2.1 系统总线仲裁方案 系统中的数据交换是由总线来实现的,因此总线的管理是一个极为重要的问题。只有恰当地把总线分配给相应的总线使用设备,系统才能稳定高效地工作。特别是在一条总线上挂接多个设备,并且它们都需要占用总线(即它们都能成为这条总线的主设备)的时候,就产生了总线的竞争问题。这时候可以通过总线仲裁来解决总线的竞争问题。通过总线仲裁,可以实现多个设备以分时共享的方式占用一条总线。在总线的仲裁方案中,常常会指定一个总线的缺省占有设备。总线的缺省占有设备是指缺省状态的总线占用者,其它设备需要使用总线的时候,可以通过总线仲裁器向该设备申请总线的使用权,使用完以后再把总线释放出来。 图4是TMS320C6202的EMIF总线挂接的外设的示意图。从图中可以看出,EMIF接口总线上挂接了以下几个设备:DSP、SRAM、FLASH、逻辑控制电路,其中DSP和逻辑控制电路可以成为EMIF接口总线的主设备。DSP复位后,默认的状态是总线的从设备,当它需要成为总线的主设备的时候,就得向外部总线仲裁器(FPGA)申请总线。主计算机需要读取图像数据时,先给FPGA发送请求,然后FPGA收回EMIF的部线控制权,PCI9054通过FPGA读取SRAM中的图像数据。图5是系统进入 正常跟踪状态时EMIF总线的占用时序图。 每一场图像处理的时序相同,其中: %26;#183;FPGA从FIFO中读取图像数据,并存储在SRAM中的时序为:周期T1=4.2ms,总线占用时间T2=0.3ms; %26;#183;DSP读取处理窗中的图像数据的时序为:距离下一场图像开始时间T3=7.95ms,总线占用时间T4=0.16ms; %26;#183;主机读取图像数据的时序为:周期T5=20ms,总线占用时间T6=2.3ms。 TMS320C6202的扩展总线上挂接的设备除了DSP外,还有PCI9054和逻辑控制电路。TMS320C6202的扩展总线的连接情况请参照图6。TMS320C6202内部的扩展总线仲裁器被禁用。扩展总线的缺省占用设备是逻辑控制电路。PIC9054要占用扩展总线就必须向逻辑控制电路申请总线占用权。 2.2.2 系统逻辑控制设计 FPGA在系统启动时根据主机发送的命令对系统进行自检,其中有对A/D转换器、FIFO等器件的复位操作;在系统进入正常工作状态时,它还需要控制FLASH和SRAM的读写,并且通过设置寄存器,让DSP和主机了解FIFO、SRAM、FLASH所处的状态,并使FPGA按要求将每帧图像数据存放在SRAM内的指定位置。

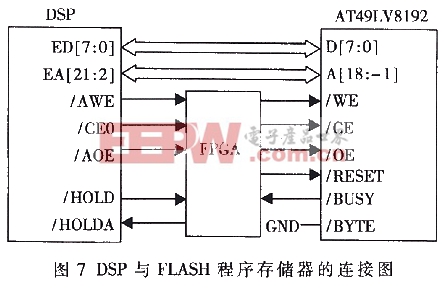

每一场图像处理的时序相同,其中: %26;#183;FPGA从FIFO中读取图像数据,并存储在SRAM中的时序为:周期T1=4.2ms,总线占用时间T2=0.3ms; %26;#183;DSP读取处理窗中的图像数据的时序为:距离下一场图像开始时间T3=7.95ms,总线占用时间T4=0.16ms; %26;#183;主机读取图像数据的时序为:周期T5=20ms,总线占用时间T6=2.3ms。 TMS320C6202的扩展总线上挂接的设备除了DSP外,还有PCI9054和逻辑控制电路。TMS320C6202的扩展总线的连接情况请参照图6。TMS320C6202内部的扩展总线仲裁器被禁用。扩展总线的缺省占用设备是逻辑控制电路。PIC9054要占用扩展总线就必须向逻辑控制电路申请总线占用权。 2.2.2 系统逻辑控制设计 FPGA在系统启动时根据主机发送的命令对系统进行自检,其中有对A/D转换器、FIFO等器件的复位操作;在系统进入正常工作状态时,它还需要控制FLASH和SRAM的读写,并且通过设置寄存器,让DSP和主机了解FIFO、SRAM、FLASH所处的状态,并使FPGA按要求将每帧图像数据存放在SRAM内的指定位置。 当FIFO处于半满状态时,控制逻辑电路收回EMIF接口总线的占用权。获得总线占用权后,开始读取FIFO中的数据,直到FIFO被读空以后才释放EMIF总线。在系统中,FIFO中的图像数据是按8位存储的,SRAM中的图像数据是按32位来组织的,所以控制逻辑电路要把从FIFO中读出的8位图像数据装配成32位数据后再写到SRAM中。 2.3 DSP程序智能加载设计 TMS320C6202有两种存储器映射方式:MAP0和MAP2。通过扩展总线的XD[4:0]利用上拉/下拉电阻进行复位时的芯片启动模式设置。系统中将存储器映射方式设置为1,即地址0处的存储器在内部,芯片自加载方式为8bit ROM方式。图7给出的是系统中设计的以一片FLASH(AT49LV8192)作为程序存储器与DSP的连接图。AT49LV8192的存储空间为1Mbyte。 由于FPGA和DSP对FLASH的操作共享,因此要实现对FLASH的编程操作必须要通过这两个设备。如果采用DSP采用编程,则需要先给DSP加载一个烧写FLASH的程序,并且需要将烧写的程序存储在数据区内,这种方法复杂而且不容易实现。本系统采用的方法是:由主机通过FPGA对FLASH进行编程。首先主机通知FPGA将要进行编程,由FPGA收回EMIF总线,并告知主机;接收主机将编程数据写给FPGA,并由它负责对FLASH执行写操作。 在系统的运行过程中,系统可以根据作战环境不同以及操作指令的不同,自适应地对DSP加载不同的程序,从而实现DSP程序动态加载设计,并增加系统的灵活性和智能化程序。其工作流程如图8所示。 即系统在启动的时候,由主控计算机对当前所处环境的图像进行特征提取,并加以分析、判断,根据判断结果从主控计算机的DSP程序算法库中选出适合当前环境特点的算法程序,来给图像处理板上的FLASH芯片进行编程,编程完毕后启动DSP的BOOTLOADER,将FLASH中的程序加载进来。这样就实现了DSP程序的自适应加载功能。

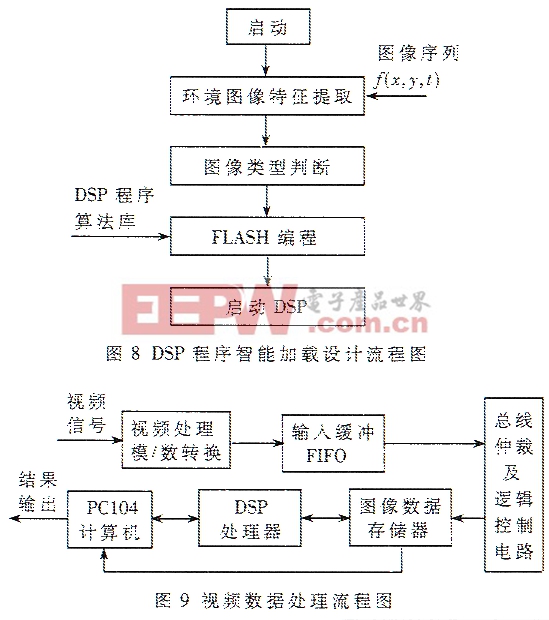

当FIFO处于半满状态时,控制逻辑电路收回EMIF接口总线的占用权。获得总线占用权后,开始读取FIFO中的数据,直到FIFO被读空以后才释放EMIF总线。在系统中,FIFO中的图像数据是按8位存储的,SRAM中的图像数据是按32位来组织的,所以控制逻辑电路要把从FIFO中读出的8位图像数据装配成32位数据后再写到SRAM中。 2.3 DSP程序智能加载设计 TMS320C6202有两种存储器映射方式:MAP0和MAP2。通过扩展总线的XD[4:0]利用上拉/下拉电阻进行复位时的芯片启动模式设置。系统中将存储器映射方式设置为1,即地址0处的存储器在内部,芯片自加载方式为8bit ROM方式。图7给出的是系统中设计的以一片FLASH(AT49LV8192)作为程序存储器与DSP的连接图。AT49LV8192的存储空间为1Mbyte。 由于FPGA和DSP对FLASH的操作共享,因此要实现对FLASH的编程操作必须要通过这两个设备。如果采用DSP采用编程,则需要先给DSP加载一个烧写FLASH的程序,并且需要将烧写的程序存储在数据区内,这种方法复杂而且不容易实现。本系统采用的方法是:由主机通过FPGA对FLASH进行编程。首先主机通知FPGA将要进行编程,由FPGA收回EMIF总线,并告知主机;接收主机将编程数据写给FPGA,并由它负责对FLASH执行写操作。 在系统的运行过程中,系统可以根据作战环境不同以及操作指令的不同,自适应地对DSP加载不同的程序,从而实现DSP程序动态加载设计,并增加系统的灵活性和智能化程序。其工作流程如图8所示。 即系统在启动的时候,由主控计算机对当前所处环境的图像进行特征提取,并加以分析、判断,根据判断结果从主控计算机的DSP程序算法库中选出适合当前环境特点的算法程序,来给图像处理板上的FLASH芯片进行编程,编程完毕后启动DSP的BOOTLOADER,将FLASH中的程序加载进来。这样就实现了DSP程序的自适应加载功能。 2.4 视频数据流分析 车载跟踪系统的视频数据处理流程如图9所示。由该图可以分析出现视频数据的转移流程: (1) 模拟视频信号从摄像机进入视频接口模块,由视频接口电路采集、处理原始视频信号,得到统一的数字视频数据和视频同步信号。 (2) 数字视频数据从视频接口模块进入输入缓冲FIFO,当FIFO到达半满状态时,由逻辑控制电路发出读取FIFO数据的请求。逻辑控制电路收回EMIF接口总线的占用权后,由逻辑控制电路读取FIFO中的数据,写入到SRAM中。在这个过程中,逻辑控制电路还要把四个8位的图像数据装配成32位的图像数据。 (3) 当逻辑控制电路向SRAM写完一帧图像数据时,首先判断DSP程序是否启动,如果未启动,则给PCI9054发出中断,请求PC104计算机处理图像数据;;否则,向DSP发出图像存放完成的中断,请求DSP处理图像数据。 (4) DSP开始从SRAM中读取数据,然后进行处理,并将处理结果通过扩展总线经由逻辑控制电路和PIC9054送到PC机。 (5) PCI接口电路通过逻辑控制电路读取SRAM中装配好的视频数据,并由它送往PC机,并结合DSP的处理结果,显示处理后的视频图像和运动目标的一些特征数据。 3 硬件平台调试及性能测试 以TMS320C6202为核心器件设计的数字图像跟踪系统充分发挥了DSP的强大运算能力和接口能力,在采用相应的跟踪算法时,可在≤8ms的时间内给出目标参数。现以最费时的模板图像匹配算法对系统运行时间进行估计。

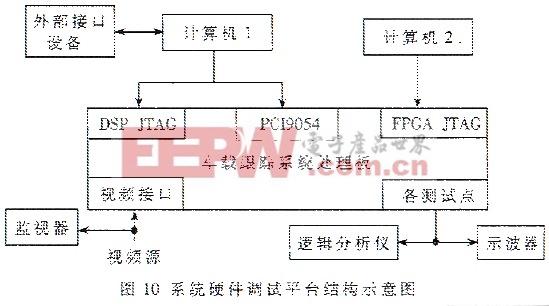

2.4 视频数据流分析 车载跟踪系统的视频数据处理流程如图9所示。由该图可以分析出现视频数据的转移流程: (1) 模拟视频信号从摄像机进入视频接口模块,由视频接口电路采集、处理原始视频信号,得到统一的数字视频数据和视频同步信号。 (2) 数字视频数据从视频接口模块进入输入缓冲FIFO,当FIFO到达半满状态时,由逻辑控制电路发出读取FIFO数据的请求。逻辑控制电路收回EMIF接口总线的占用权后,由逻辑控制电路读取FIFO中的数据,写入到SRAM中。在这个过程中,逻辑控制电路还要把四个8位的图像数据装配成32位的图像数据。 (3) 当逻辑控制电路向SRAM写完一帧图像数据时,首先判断DSP程序是否启动,如果未启动,则给PCI9054发出中断,请求PC104计算机处理图像数据;;否则,向DSP发出图像存放完成的中断,请求DSP处理图像数据。 (4) DSP开始从SRAM中读取数据,然后进行处理,并将处理结果通过扩展总线经由逻辑控制电路和PIC9054送到PC机。 (5) PCI接口电路通过逻辑控制电路读取SRAM中装配好的视频数据,并由它送往PC机,并结合DSP的处理结果,显示处理后的视频图像和运动目标的一些特征数据。 3 硬件平台调试及性能测试 以TMS320C6202为核心器件设计的数字图像跟踪系统充分发挥了DSP的强大运算能力和接口能力,在采用相应的跟踪算法时,可在≤8ms的时间内给出目标参数。现以最费时的模板图像匹配算法对系统运行时间进行估计。 设匹配模板为16%26;#215;16,匹配搜索范围为48%26;#215;48,逐点匹配,以MAD准则为匹配准则,每个像素点的计算需要四条DSP指令,指令周期为4ns。则系统运行结果为: 每次匹配运算的像素个数为:16%26;#215;16; 搜索区内匹配次数为:(48-16)%26;#215;(48-16)=32%26;#215;32; 总匹配运算时间为:16%26;#215;16%26;#215;32%26;#215;32%26;#215;4%26;#215;4ns≈4.19ms。 可以看出,系统的运算能力满足系统处理图像数据的需求。 整个系统的调试工作可以分为硬件调试、软件调试、软硬件硬调三个部分。硬件系统的调试从总体上看可分为两个部分:硬件系统的基本测试和各个功能模块的调试。图10给出的是硬件系统的调试平台。 在调试过程中,硬件系统的功能调试可划分为以下几个部分:视频接口、输入缓冲FIFO的读写操行、DSP程序存储器FLASH的读写操作、图像帧存储器的读写操作、DSP与PCI9054的HPI接口、主计算机和PCI9054的读写操作等调试。通过编写相关的调试程序可验证硬件电路的正确性。 基于DSP的智能图像跟踪系统在继承成熟技术的基础上,运用先进的图像处理和模式识别技术,采用高速DSP处理器、双CPU并行处理的模式,确保了系统运行可靠、跟踪精度高,具有很好的抗干扰、抗复杂背景的能力。将图像跟踪系统应用在装甲战车上,使其和战车指挥系统整合为一个完整的数字式系统,将是装甲战车发展一个必然趋势。可以预见,此系统的研制成功及在装甲车辆上的广泛应用,将大大推动装甲车辆的技术进步。

设匹配模板为16%26;#215;16,匹配搜索范围为48%26;#215;48,逐点匹配,以MAD准则为匹配准则,每个像素点的计算需要四条DSP指令,指令周期为4ns。则系统运行结果为: 每次匹配运算的像素个数为:16%26;#215;16; 搜索区内匹配次数为:(48-16)%26;#215;(48-16)=32%26;#215;32; 总匹配运算时间为:16%26;#215;16%26;#215;32%26;#215;32%26;#215;4%26;#215;4ns≈4.19ms。 可以看出,系统的运算能力满足系统处理图像数据的需求。 整个系统的调试工作可以分为硬件调试、软件调试、软硬件硬调三个部分。硬件系统的调试从总体上看可分为两个部分:硬件系统的基本测试和各个功能模块的调试。图10给出的是硬件系统的调试平台。 在调试过程中,硬件系统的功能调试可划分为以下几个部分:视频接口、输入缓冲FIFO的读写操行、DSP程序存储器FLASH的读写操作、图像帧存储器的读写操作、DSP与PCI9054的HPI接口、主计算机和PCI9054的读写操作等调试。通过编写相关的调试程序可验证硬件电路的正确性。 基于DSP的智能图像跟踪系统在继承成熟技术的基础上,运用先进的图像处理和模式识别技术,采用高速DSP处理器、双CPU并行处理的模式,确保了系统运行可靠、跟踪精度高,具有很好的抗干扰、抗复杂背景的能力。将图像跟踪系统应用在装甲战车上,使其和战车指挥系统整合为一个完整的数字式系统,将是装甲战车发展一个必然趋势。可以预见,此系统的研制成功及在装甲车辆上的广泛应用,将大大推动装甲车辆的技术进步。

评论