基于C6000系列DSP的MPEG-4编码器实现

MPEG-4是一种开放性标准,其中许多部分都没有规定,可以加入一些新的算法,因此采用通用DSP能够随时更新算法、优化算法、使得编码效率更高。由于MPEG-4编码算法复杂,需要存储的数据量大,无论是存储空间分配、数据传输还是运算速度对DSP来说都是挑战。本文介绍了基于C6000系列DSP的MPEG-4视频编码卡的软硬件实现。利用DSP的VLIW和流水线结构设计程序可以使MPEG-4编码效率大大提高。

1 DSP特性介绍

由于算法的复杂性及数据量的日益增大,单靠串行结构的处理器完成数据处理工作已经越来越不可行,因此出现了并行结构的CPU以完成这一新的任务。现今最著名的两种并行体系结构是超长指令字VLIW(Very Long Instruction Word)结构和超标量体系结构。由于超标量体系结构CPU硬件极其复杂,指令动态调度将导致时间的不确定性,所以DSP很少使用这种结构。而一般使用超长指令字(VLIW)结构,这种长指令通常包括多个彼此独立的同步操作。

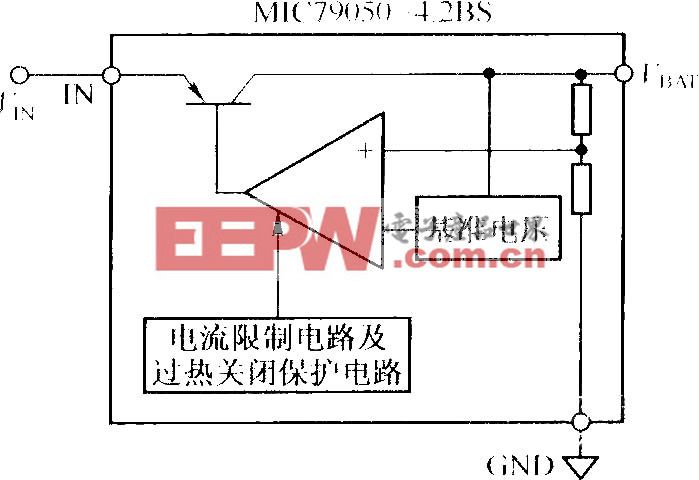

DSP的CPU结构如图1所示,它具有两个通道,每个通道具有4个功能单元(1个乘法器和3个算术逻辑单元),16个32位通用寄存器,每个通道的功能单元可以随意访问本通道的寄存器。CPU还有两个交叉单元,通过它们,一个通道的功能单元可以访问另一个通道的寄存器。另外CPU还具有256bit宽的数据和程序通道,可以使程序存储器在每个时钟周期提供8条并行执行指令。这种CPU结构是DSP具有VLIW结构的最基本条件。此系列DSP的存储空间映射为内部存储器、内部外设及扩展存储器。其中内部存储器由64KB内部程序存储器和数据存储器构成,内部程序存储器可以映射到CPU地址空间或者作为Cache操作。内部和外部数据存储器均可通过CPU、DMA或HPI(HostPort Interface)方式访问,HPI接口使上位机可以访问DSP的存储空间。

评论