基于DSP的机载视频图像实时压缩与处理系统

由于受到无线传输带宽的限制, 无人机对地面目标侦察获得的高分辨率视频图像必须经过有效压缩才能实时传输给地面接收处理系统。现有的视频压缩标准有H.261、H. 262、H . 263 及MPEG-1、MPEG-2、MPEG-4 等。

其中MPEG-4 由于采用基于对象的压缩编码方法, 较之以往各标准的基于帧的压缩编码方法, 其时间和空间冗余更低, 在保持解码质量的同时提高了压缩率。MPEG-4 还具有更好的交互性能及更强的抗误码性能 , 较之以往的压缩标准, 更适合无线信道的传输。

视频压缩算法比较复杂, 加之无人机有效载荷的重量和体积限制, 难以实现对机载视频图像的实时压缩编码,通常只能低分辨率图像实时压缩。本文基于TI 公司最新推出的媒体处理器TMS320DM642 设计并实现了机载图像实时压缩编码与处理系统, 实现了对最高分辨率为D1分辨率机载视频图像的分辨率和压缩比可调的MPEG-4实时压缩处理及恒定码流的输出。

1 设计要求

整个压缩处理系统完成对机载高分辨率摄像机输出的PA L 制式模拟视频信号进行实时采集、压缩与传输。

为了便于地面接收处理系统实时地分析图像, 须将无人机拍摄图像的时间及空间位置等附加信息和压缩图像数据实时地打包。MPEG-4 为不等长压缩编码, 为便于无线传输, 需将MPEG-4 数据包流进行编帧, 形成256 KB/ s的恒定基带码流, 实时传输给无线信道子系统供调制发射。系统还需根据控制命令动态地改变图像的分辨率及压缩比。

2 系统硬件设计

2. 1 TMS320DM642 芯片的特点

DM642 属于TMS320C64x 系列DSPs。Veloci T I 结构使C6000 DSPs 在视频和图像处理中得到广泛应用。

CPU 的VLIW 结构由多个并行运行的执行单元组成, 这些单元在单个周期内可执行多种指令。并行是C6000 获得高性能的关键。C64x 在C6000 的基础上有一些重要的改进。除了有更高的时钟频率外, C64x 从以前的VelociTI 结构扩展到Veloci TI. 2 结构, 包含了许多新的指令,增加了额外的数据通道, 寄存器的数量也增加了一倍。这些扩展使得CPU 可以在一个时钟周期内处理更多的数据, 从而获得更高的运算性能。

DM642 芯片集成了各种片内外设, 使得开发视频和图像领域的应用更为方便。它带有3 个可配置的视频端口, 提供与视频输入、视频输出以及码流输入的无缝接口。

这些视频端口支持许多格式的视频输入/ 输出。利用DM642 开发视频编码器, 其视频输入部分只需要一块视频采集芯片即可, 如AD 公司的A DV7181, 无需外加逻辑控制电路和FIFO 缓存, 使硬件系统更为简单和稳定。

DM642 集成的64 位的无缝外部存储器接口( EMIF) , 能够实现与外部同步和异步存储器或外设的无缝连接。

DM642 的其他外设包括: 10 Mbps/ 100 Mbps 的以太网口( EMAC) 、多通道音频串口(McASP) 、主机接口( HPI) 、多通道缓冲串口( McBSP) 以及PCI 接口等。

2. 2 系统硬件组成

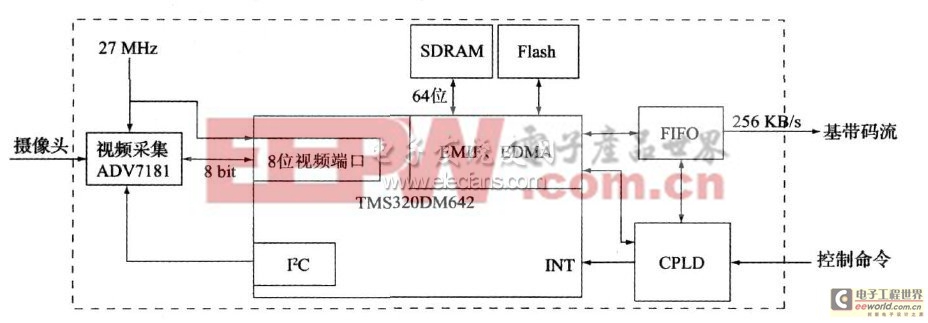

机载图像实时压缩与处理系统以TMS320DM642 高性能通用DSP 芯片为核心, 由视频输入采集模块、图像压缩处理模块、外部存储模块及传输控制接口模块组成。其硬件系统框图如图1 所示。

图1 机载视频图像实时压缩处理系统硬件框图

图像采集模块对输入模拟视频信号进行同步捕获、采集和视频解码。视频解码器输出的数据格式为YUV4: 2:2。视频解码数据通过DMA 通道向DM642 VPORT 通道缓冲单元发送数据, 当采集完一帧数据时产生DMA 中断。图像压缩处理模块根据接收到的控制命令将视频解码数据进行实时压缩数理后缓存到存储模块中。存储模块采用32 MB 64 位的SDRAM, 实现程序和数据的存储。

传输控制接口模块将缓存在SDRAM 中的待传输码流以256 KB/ s 的恒定速率8 位并行传输至输出端口, 并接收地面发送的控制命令。该模块由FIFO 芯片和CPLD 组成, FIFO 半空时向DSP 发送中断信号。

评论