FPGA的配置及接口电路

FPGA的配置方式分为主动式和被动式,数据宽度有8位并行方式和串行方式两种。在主动模式下,FPGA在上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射;而在被动模式下,FPGA则作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。 1配置引脚

FPGA的配置引脚可分为两类:专用配置引脚和非专用配置引脚。专用配置引脚只有在配置时起作用,而非专用配置引脚在配置完成后则可以作为普通的I/O口使用。

专用的配置引脚有:配置模式脚M2、M1、M0;配置时钟CCLK;配置逻辑异步复位PROG,启动控制DONE及边界扫描TDI,TDO,TMS,TCK。非专用配置引脚有Din,D0:D7,CS,WRITE,BUSY,INIT。

在不同的配置模式下,配置时钟CCLK可由FPGA内部产生,也可以由外部控制电路提供。

2 FPGA的配置模式

FPGA共有四种配置模式:从串模式(Slave Serial),主串模式(MasterSerial),从并模式(Slave Farallel/S e 1 e c tMap)以及边界扫描模式(Boundary-Scan)。具体的配置模式由模式选择引脚M2、M1、M0决定。表1为不同的配置模式所对应的M2、M1、M0,配置时钟的方向以及相应的数据位宽。

3配置过程

(1)初始化

系统上电后,如果FPGA满足以下条件:Bank2 的I/O输出驱动电压Vcc0_2大于lv;器件内部的供电电压Vccint为2.5v,器件便会自动进行初始化。在系统上电的情况下,通过对PROG引脚置低电子,便可以对FPGA进行重新配置。初始化过程完成后,DONE信号将会变低。

(2)清空配置存储器

在完成初始化过程后,器件会将INIT信号置低电平,同时开始清空配置存储器。在清空完配置存储器后,INIT信号将会重新被置为高电平。用户可以通过将PROG或INIT信号(1NIT为双向信号)置为低电平,从而达到延长清空配置存储器的时间,以确保存储器被清空的目的。

(3)加载配置数据

配置存储器的清空完成后,器件对配置模式脚M2、N1、M0进行采样,以确定用何种方式来加载配置数据。

(4)CRC错误检查

器件在加载配置数据的同时,会根据一定的算法产生一个CRC值,这个值将会和配置文件中内置的CRC值进行比较,如果两者不一致,则说明加载发生错误,INIT引脚将会被置低电平,加载过程被中断。此时若要进行重新配置,只需将PROG置为低电平即可。

(5)START-UP

START-UP阶段是FPGA由配置状态过渡到用户状态的过程。在START-UP完成后,FPGA便可实现用户编程的功能。在START-UP阶段中,FPGA会进行一下操作:

①将DONE信号置高电平,若DONE信号没有置高,则说明数据加载过程失败;

②在配置过程中,器件的所有I/O引脚均为三态,此时,全局三态信号GTS置低电平,这些I/O脚将会从三态切换到用户设置的状态;

③全局复位信号GSR置低电平,所有触发器进入工作状态;

④全局写允许信号GWE置低电平,所有内部RAM有效;

整个过程共有8个时钟周期C0-C7。在默认的情况下,这些操作都和配置时钟CCLK同步,在DONE信号置高电子之前,GTS,GSR,GWE都保持高电平。

4 SelectMap并行配置模式

Virtex系列FPGA是Xilinx公司的一款高密度,大容量的现场可编程门阵列,其最大容量可达100万门,最高工作频率可达200M,支持多达16种I/O标准,内置了4个BLOCKRAM。这些特性使它在数字图像处理,通信等领域得到了广泛的应用。

SelectMap模式是一种8位并行配置模式,它是Virtex系列FPGA最快的一种配置模式,其配置时钟最高可达66MHZ,每个配置时钟周期内有8位配置数据下载到FPGA内。在对配置速度要求较高的一些应用场合,一般使用SelectMap模式。

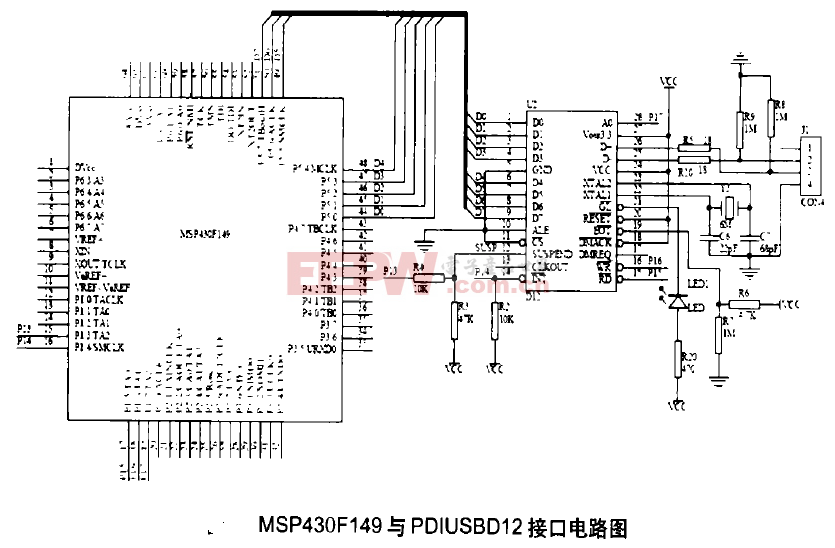

SelectMap端口是一个8位双向数据端口,通过它实现对Virtex的配置。利用SelectMap对Virtex进行配置时,共有8个数据信号D0-D7和7个控制/状态信号,分别为:CCLK,PROG,DONE,INIT,CS,WRITE,BUSY。

对Virtex进行并行配置,应用最为广泛的接口电路便是CPLD+并行EPROM。

由于FPGA管脚内部有上拉电阻,因此,当管脚悬空时,便是高电平。

CPLD所要实现的功能模块包括:地 址发生器,写控制寄存器,三态缓冲。 其中,PROG为全局复位,DONE为全局 三态控制,INIT和BUSY用来控制地址 发生器;地址发生器的总线位宽由存储器的容量决定,若EPROM的容量为1MByte,则地址总线需要20位;在配置阶段,CS和WRITE引脚必须置低电平。

对VIRTEX系列的FPGA而言,其配置时钟最高可达66MHZ,但是,在一般情况下,配置时钟是达不到66MHZ的,它由PROM的存储时间(tACC)和FPGA配置数据的建立时间(tSMDCC)决定的:晶振频率:1/(tACC+TSMDCC)。VIRTEX的TSMDCC为2.0ns,EPROM的存取时间通常为l00ns,在这种情况下,配置时钟为9.6MHZ,要远远低于66MHZ,因此,提高配置速度关键是要选用存取速度快的EPROM。

5串行菊花链配置方式

串行菊花链配置方式是指将配置数据从串行PROM顺序下载到主FPGA器件和从FPGA器件中。配置时钟CCLK由主FPGA器件提供。

主器件将会被首先配置,在主器件配置完成前,其Dout引脚是没有数据输出的,从器件处于空闲状态。在主器件配置完成后,其Din,Dout便形成直通状态,配置数据通过主器件的Dout进入从器件的Din,对从器件进行配置。

由于菊花链配置方式要求只能有一个用于下载的位流文件,因此,需要在软件开发环境中利用PROM文件生成工具将将主器件和从器件的配置位流文件合成为一个文件。

主器件在配置完成后,并不立即启动,进入工作状态。只有菊花链中所有FPGA的DONE引脚都被置为高电平时,即所有的配置数据都下载到相应的FPGA中,各个器件才会启动,其各自的全局三态结束GTS、全局复位GSR、全局写允许GWE才会置低电平。因此,虽然主从器件的配置是有先后顺序的,但基本上它们是同时进入工作状态的。 6结束语

使用并行EPROM对FPGA进行配置时,速度相对较快,存储容量较大;而在一些对空间较为敏感,速度要求不太高的应用中,利用串行方法进行配置,可以减小电路板的面积,同时可以简化系统结构。

评论