基于ISA总线的通用多DSP目标系统

(1)目标系统的地址分配与实现

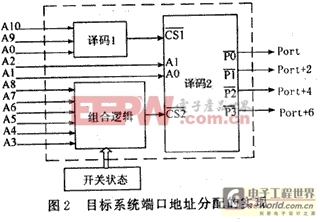

每块DSP目标板只占用一组端口地址,每组地址共4个:数据端口、地址端口、复位端口和控制端口。组起始地址通过4b跳线开关加以选择,设开关值为n,则板卡起始地址为360-4×n(记作port),其他3个端口地址分别为port+2,port+4,port+6。在FPGA中采用如图2所示的逻辑,实现了目标系统板端口地址的动态分配。

|

数据端口port 用于实现对DSP内部存储器的读写操作,完成DSP与上位机之间的数据传输。

地址端口port+2 用于提供对DSP进行读写操作时DSP内部程序存储区(PM)或数据存储区(DM)的起始地址。

复位端口port+4 用于对DSP进行复位操作,实现对DSP的软复位。

控制端口port+6 用于选择要操作的DSP。

(2)控制信号的形成

目标板上6片DSP占用同一端口地址,系统工作时,可以对任意DSP的任一数据区进行读写操作。对DSP的片选信号是通过对控制端口的操作来实现的。当A2A1=11时,对应于DSP的控制端口,这时数据线的低3位(DATA[2..0])用于指定6个DSP中的一个。

4 下载软件设计

ADSP2181片内集成了一个可以访问其内部存储器的16 b IDMA端口,主机通过此端口可以访问ADSP2181片内的程序存储器和数据存储器的任一单元,实现对DSP下载文件、传输数据等操作,这一过程是通过上位机对DSP的IDMA端口的操作来完成的。本文设计了基于VB的通用多DSP目标系统的下载软件,通过上位机对目标系统进行各种操作。

(1)端口选择 选择一组端口地址,他应与目标板的端口地址相一致;

(2)处理器选择 选择所要进行读写操作及下载的处理器号(1#~6#);

(3)下载文件选择 选择要加载到指定DSP的程序;

(4)下载 执行下载操作,并自动检查加载是否成功,若不成功,则重新加载;

(5)读处理器选择 调用读处理器模块,读选定处理器的指定单元的内容;

(6)写处理器选择 调用写处理器模块,在所选的处理器的指定单元写入数据。

5 结 语

通用多DSP目标系统,在地址分配上充分考虑到了ISA总线和定点ADSP2181的特点,采用地址的动态分配技术,有效地节省了系统的资源。下载软件可以对1片或多片DSP进行文件下载、读、写等操作,极大地增强了系统的通用性与灵活性。该系统可用于各种算法的硬件平台和早期研发,具有较高的应用价值。

评论