PCI总线目标控制器的设计

0引言

PCI(PeripheralComponentInterconnect)总线是微型计算机中处理器/存储器与外围控制部件、扩展卡之间的互联接口。PCI总线规范是互联机构的协议,以及电气和机械配置的规范,是当今高性能微型计算机事实上的总线标准。[1]

PCI总线控制器为PCI总线和用户设备提供操作接口,协调PCI总线信号和用户设备接口信号,使用户设备能够按照PCI总线的规范进行数据的传输。本文设计了一个适用于CMOS图象处理的PCI目标控制器,具有较强的通用性。

1控制器的顶层设计

PCI总线目标设备在总线传输中处于被动地位,它不会申请对总线的使用权。当PCI总线上的某一主设备发起对本地资源的访问时,整个控制逻辑的建立和数据传输的过程都是通过目标控制器实现的。

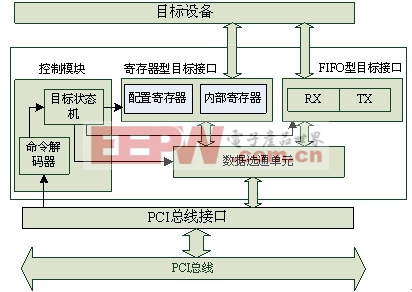

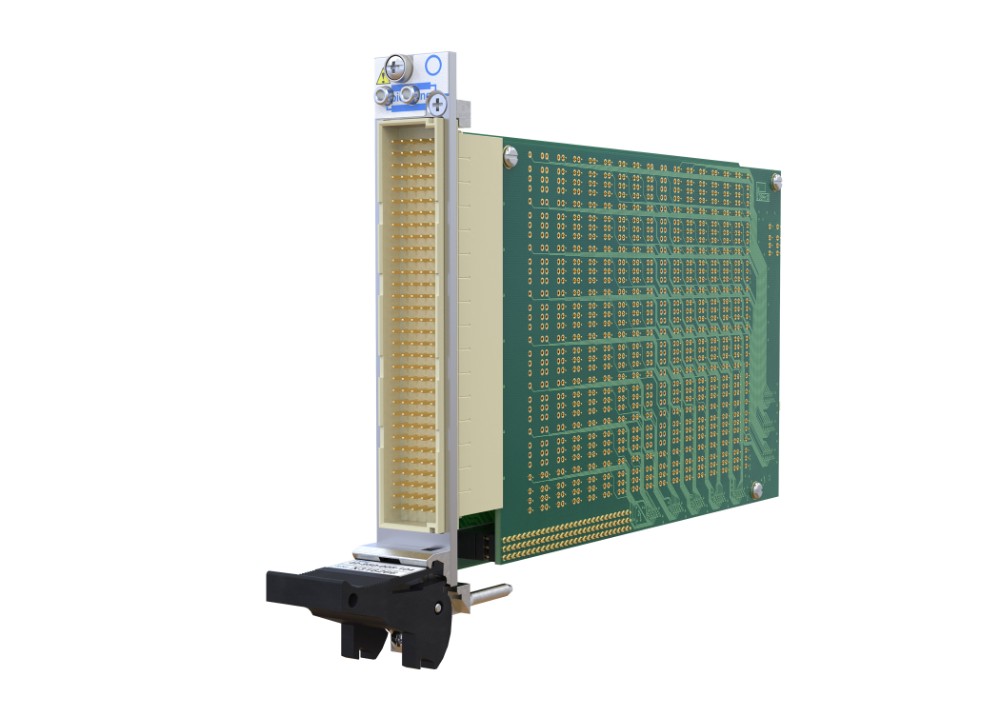

PCI系统中,目标设备在地址周期内响应总线主设备的传输要求,并配合主设备完成整个数据传输。图1为目标控制器的详细结构图。

本设计将目标控制器按照功能分为几个功能模块实现,即命令解码器、状态机、FIFO类型目标接口和寄存器型目标接口。命令解码模块和状态机构成目标控制器的控制部分,PCI主设备发起某类型的操作,目标控制器在地址周期内解析相应的地址和命令信息。在解析地址确定为本次操作的目标设备后,目标控制器会启动目标设备状态机根据当前解码的信息进行一系列的控制操作。FIFO类型通道用于大批量的数据传输,可将本地存储器块挂接在该类型的数据通道上;寄存器类型接口用于数据量小的数据传输,该接口的后面可以挂接配置寄存器和一些本地功能设备的控制/状态寄存器块。这样,PCI总线上的主设备既可以访问到本地的存储器设备也可以访问本地的寄存器。下面从目标控制器的数据路径和控制路径分别进行论述。

2控制模块实现

目标控制器的控制由两部分完成,命令解码器和目标状态机。命令解码器解码来自PCI总线上的地址命令信息作为目标状态机的输入,状态机鉴于此输入执行相应的操作。

(1)命令解码器:PCI总线主设备在地址周期内通过命令数据线(C/BE#)设置不同的编码可以发起以下的操作,I/O读写、存储器读写、配置读写、存储器行读/多行读和存储器写及使无效。

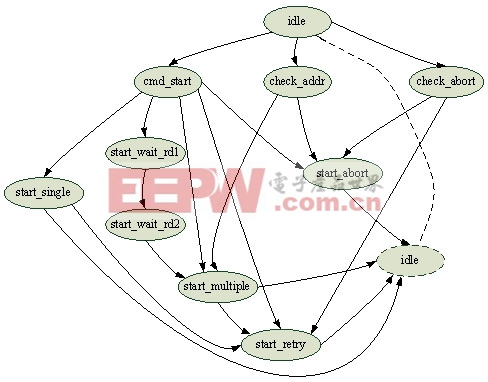

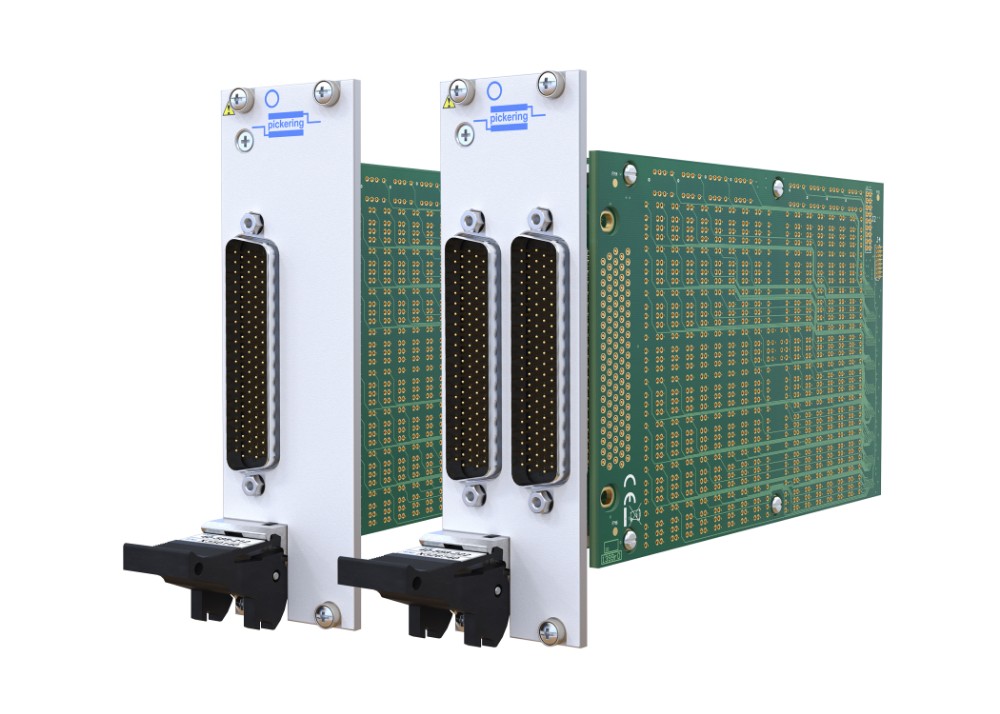

(2)目标状态机[3]:对于PCI总线上传来的信号,状态机根据命令解码器的解码信息来控制总线控制器进行相应的操作。如果地址信息不正确或者本地的设备正忙于存取数据,状态机会向PCI总线上发起本次操作的主设备回应目标丢弃或目标重试。目标状态机的具体设计,如图2所示。

评论