基于CPCI总线的FPGA加载设计

0 引言

由于具有极强的实时性和并行处理能力,FPGA芯片在无线通信、信号处理等领域得到了广泛应用。

作为一种半定制电路,FPGA 的使用非常灵活,对于同一片FPGA,通过加载不同的编程数据可以产生不同的电路功能。但是,由于基于静态只读存储器(SRAM,Static Random Access Memory)的架构,FPGA 掉电后就变为白片,再次上电时需要EPROM 芯片对其进行加载。对于需要切换算法的场景,就需要通过上位机对其进行动态加载。本文在深入分析了FPGA 配置流程和理解CPCI 总线的基础上,设计实现了基于CPCI 总线的FPGA 动态加载。

1 硬件设计

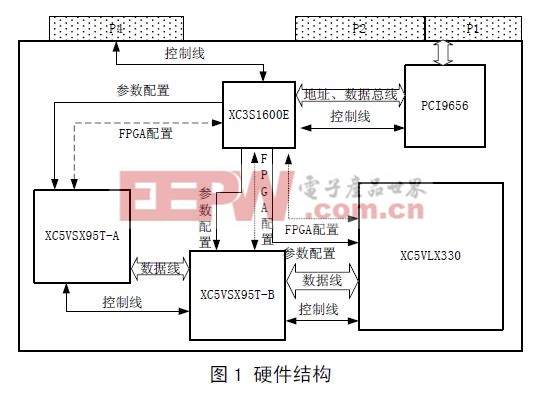

系统中需要对三片Virtex5 系列的芯片进行动态加载,整个硬件结构框图如图1 所示。Spartan-3E与PCI9656直接相连,作为主控制芯片Spartan-3E一方面接收来自CPCI 总线的数据,对V5 芯片进行参数下载、动态加载等;另一方面接收V5 芯片的传递来的各类数据,根据上层软件的请求,将各类状态信息或实时处理数据上传到工控机。

2 PCI9656 芯片介绍

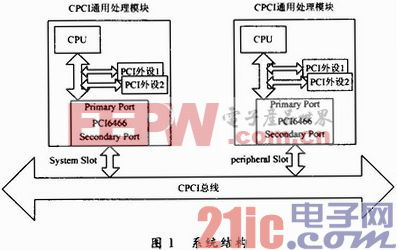

PCI 接口协议比较复杂,接口电路实现起来较为困难,在设计基于PCI或CPCI总线的数字设备时,采用各公司提供的通用PCI I/O 芯片或IP 核,可简化复杂的PCI 接口设计。PCI9656 是PLX 公司为高速PCI 总线应用而设计的通用I/O 芯片,PCI9656配备DMA 引擎、可编程直接主控和直接从属数据传输模式以及PCI 信息传输功能。零等待状态突发操作,PCI 总线突发传输速度高达528 MB/s,局域总线突发传输速度高达264 MB/s.

评论