基于FPGA的可复用SPI接口设计

master核系统输入时钟clk-in通过divider分频产生clk-out,通过改变divider的值,可以实现任意分频的时钟输出[4]。其频率表达式如下:

用verilog语言描述时钟产生模块,用ISE综合后,其生成电路如图2所示。

3.2.2. 串行接口模块spi-shift设计

数据传输模块是SPI的核心模块。此模块负责把并行进来的数据串行传出,串行进来的数据并行传出。本文设计的shift与通常的SPI移位模块设计不同,原因在于这里考虑了寄存器的复用,以使用较少硬件资源来增大一次传输数据的位数,从而提高数据传输的整体速率。对于并行进来的数据位宽比较长,比如128 位的数据时,为了提高传输的速度,本文设计工作中牺牲了资源改进了以前的保守的SPI模块。SPI MaSTer 核在主机侧作为slave设备接收数据,同时作为master设备发送数据。此模块verilog代码经ISE综合后如图3 所示。

图3.串行接口模块电路

3.2.3. 顶层TOP模块

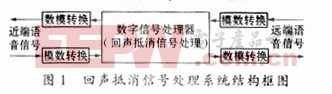

本文在分析协议的基础上建立了高速可复用SPI总线的基本结构,包括时钟生成模块,数据传输模块,并用上层TOP模块调用底层的两个模块。顶层模块的重要作用就是让分模块能够顺利的运作起来。所以此 SPI核的顶层模块要写入控制字,通过状态机控制调用时钟生成模块和数据传输模块正常运行。其经ISE综 合后如图4所示。

图4.顶层TOP模块电路

4、仿真与验证

仿真与验证是IP核设计中非常重要的一部分,因为它直接关系着IP的可用性。将用verilog 描述好的SPI 接口电路用ISE进行综合,然后用modelsim 软件进行仿真[5]。在建立测试平台时,首先要建立模拟Wishbone 协议的master模块,同时建立模拟SPI协议的slave模块,再将接收/发送数据和地址进行比较、校验。因此 Spi-top Testbench总体架构可分为:Wishbone master model、SPI master core、SPI slave model 三个模块。

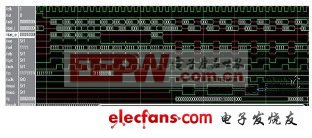

为了简单仿真8bit数据传输,首先进行复位,然后设置寄存器,再进行寄存器校验,无误之后进行8bit 数据传输,在tx上升沿发送数据,rx下降沿接收数据,仿真波形如图5所示。同理可以仿真64bit、128bit等 数据传输仿真波形。

图5. 8bit数据传输仿真波形

用ISE软件进行编译,将生成的网表文件通过JTAG下载到xilinx 公司的spartan3 系列FPGA运行,在ISE 的辅助分析下得到了正确的结果。

5、结束语

随着半导体技术的进步,FPGA 的价格越来越便宜, 工作频率越来越高,使用FPGA 实现SPI 通信 接口是切实可行的。

本文作者创新点:设计过程中很多变量都采用参数形式,具体应用于工程实践时根据实际需要更改参数即可,充分体现了可复用性。由于SPI对传输时序要求非常严格,所以本文工作中设计了一种比较可靠,稳定的时钟生成模块,它对于奇偶分频的情况分别考虑,从而避免了以往SPI总线中对系统时钟奇分频时会出现分频出的时钟不稳定的问题。数据传输模块采用较简洁的并串互转结构,一次最多可传输128位,速度是遵守SPI协议的同类器件里较快的。并且从128位到8位可选具体一次要传输多少位,有别于以往一 次传输的位数为定值的情况。

评论