机载冗余图像处理系统的设计与实现

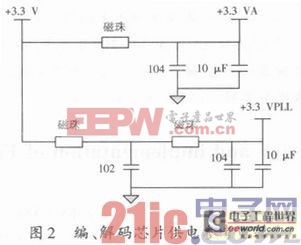

在硬件电路设计中,还需要考虑高频特性对信号的影响。整个系统显示的分辨率为1 600x1 200@60Hz,信号位为真彩色24 b,采用奇偶方式,参考时钟162 MHz,DVI编码时钟为10×162 MHz=1.62 GHz,其编码码元理论宽度仅为t=1/1.62 Hz=0.62 ns,则码元的最大变化时间应在0.62/4=0.16 ns之内。考虑数据传输的可靠性和稳定性,采用双像素传输,可以大大降低信号采样频率。此外,还要考虑到PCB布局地线的完整性和供电去耦特性。其编解码芯片混合信号的供电参考电路如图2所示。

2 SDRAM视频缓存设计

2.1 SDRAM选择依据

整个系统显示的分辨率为1 600x1 200@60 Hz,信号位为真彩色24 b,则一帧图像所需需要存储的容量C=1 600×1 200×24=46 080 000 b≈47 Mb;考虑到SDRAM乒乓操作和容量等问题,选用MICRO公司生产的容量为128M的MT48LC4M3282TG-6器件,速度等级6,时钟频率达到166 MHz。该器件具有32根数据线和12根地址线,还有一些控制线。通过在FPGA内部搭建逻辑控制单元,可以很好的控制SDRAM视频信号的翻转等操作。

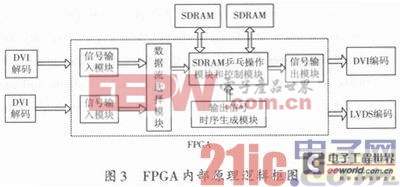

2.2 FPGA内部原理逻辑框图

FPGA内部原理逻辑框图如图3所示。

2.2.1 FPGA内部逻辑功能介绍

(1)信号输入模块

这部分的主要功能是接收外部输入的视频信号,增强输入信号的驱动能力,为信号的后续处理做准备。其用Verilog语言实现的逻辑代码如下所示:

(2)数据流选择模块

根据需要选择两路输入视频信号中的一路进行输出。

(3)SDRAM乒乓操作和控制模块

由于SDRAM乒乓操作具有节省缓冲区空间、流水线式算法以及低速模块处理高速数据流的特点。因此,本设计采用乒乓操作SDRAM。

SDRAM作为整个图像处理系统的缓存,起着至关重要的作用。它将外部输入的图像按帧存入SDRAM中,然后按帧将图像数据送到外部继续处理。FPGA的控制逻辑所需要完成的功能有:接收来自外部的图像数据,并进行缓冲和数据重组,产生符合SDRAM控制器位宽的数据信号;产生对SDRAM的读、写命令和地址,并将它们寄存在FIFO中,随时供SDRAM控制器提取。因此,系统需要一个地址产生逻辑;对SDRAM进行直接控制,将用户产生的地址命令进行解析,产生读/写、刷新等一系列操作,对SDRAM发出的各种命令要符合特定的时序要求。在上电的时候还必须完成对SDRAM的初始化工作;建立用户与SDRAM的数据通道,在SDRAM和用户接口之间传递需要写入或者读出的数据,并且调整对应读/写操作的DQS信号时序,使其满足SDRAM的要求;缓存从SDRAM中读出的数据,由于直接读出的速度非常高,直接处理会对后端产生很大的压力。因此,需要进行缓存之后才送到后续处理。

评论