一种基于FPGA的视频图像画面分割器设计

本文引用地址:http://www.eepw.com.cn/article/236794.htm

由图可知:接收到输入信号后,根据视频数据提取原理,检测有效的视频数据,每来一个时钟,接收一个视频数据存储到RAM模块中;然后对RAM模块中存放的数据取平均值;接着对这些平均值隔行隔点提取,把提取出的数据送入异步FIFO中,方便读写入DDR2 SDRAM中。

隔行隔点提取有效数据就是要将一些像素丢弃,本设计采用邻域平均法来改善缩放后的视频图像质量。邻域平均法的原理是将原图中一个像素值和它周围邻近8个像素值相加,然后将求得的平均值(除以9)作为新图中该像素的值。它采用模板计算的思想,模板操作实现了一种邻域运算,即某个像素点的结果不仅与本像素有关,而且与其邻域点的像素值有关。邻域平均法的数学公式表达为:

其中f(i,j)为给定的图像,经过邻域平均处理后的图像为g(i,j),M是所取邻域中各邻近像素的坐标N是邻域中包含的邻近像素的个数。

1.2.2 图像合成和编码模块设计

1)图像合成原理

在像素域的多画面合成中,首先,对原图像按像素进行抽取,分别将多路图像按照一定的比例缩小。然后,按照一定的规则将多路图像进行排列,排列后的图像即为多路合成的图像。最后,将合成的图像编码输出,即可在同一个屏幕显示多个画面,完成对多路图像的合成。

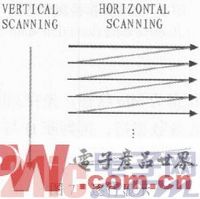

合成后的视频图像是逐行显示的,而对于将图像以逐行方式“绘制”到屏幕上的设备,每张图像都是从显示器的左上角开始,一直向右移动,直到到达显示器的右边缘为止,然后向下扫描一行,重复地从左到右进行扫描,这个过程一直持续到整个屏幕全部被刷新一次为止,如图7所示。

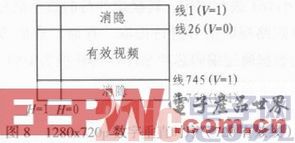

SiI1161输出的完整的一帧图像数据结构如图8所示。

以四路为例,首先,要分别对原图像进行1/4比例缩小。一帧视频图像有效显示的图像数据为26~745行,则在垂直方向上隔行抽取有效视频行,使垂直方向缩小为原来的1/2。

在水平方向上,每行有效视频由1 280个像素组成,每隔一个像素抽取一个有效视频,使水平方向缩小为原来的1/2。这样经过垂直和水平方向的抽取所得到的图像缩小为原图像的1/4。

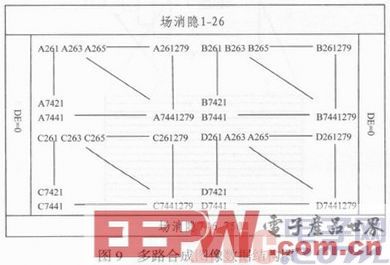

然后,按照一帧图像数据的排列格式对抽取的各路图像的像素进行排列。抽取的第一路图像的行与第二路图像的行组成一整行,第三路图像的行与第四路图像的行组成一整行,四路图像的行组成新的一帧图像的图像数据。

最后,将四路合成图像数据经过SiI164编码输出,通过逐行扫描在一个显示器上显示四路图像,即完成了四路视频图像合成。

2)图像合成模块设计

视频图像画面合成的实现方法主要分为两大类:像素域合成和压缩域合成。基于系统的图像数据为24位R、G、B数字视频格式,所以在视频图像画面合成中采用像素域内多画面合成的方法。四路视频图像合成的实现过程如下:

首先,分别在垂直方向和水平方向上抽取有效的视频数据,将四路图像各缩小为原图像的1/4。这部分功能由有效视频数据提取模块实现,该模块在前面已经做过详细介绍。然后将提取的各路图像数据按找一定顺序排列,即按照一定的规律存储到DDR2 SDRAM中。各路图像数据的地址按照上一节介绍的地址产生方法实现,都有各自固定的存储空间。

在完成各路视频图像的抽取,存储后,就要对抽取的各路视频图像的进行四画面合成。根据720P系统数字信号的数据格式,把有效视频数据从存储器中采用顺序读取出来,在相应的H、V、DE信号的位置,送视频编码输出,完成四路视频图像的合成。在合成的过程中,H、V、DE信号及时钟信号都由第一路输入的视频信号产生。四路视频合成图像的排列方式如图9所示。

2 调试结果

经过软硬件的综合调试,整个视频图像画面分割系统便可以正常工作了。

采集的多路视频图像经过FPGA图像合成处理后,可以在一个显示器显示多路视频图像。

3 结束语

文中采用FPGA开发技术实现了视频图像画面分割器的画面分割的功能。研究的主要特色在于构建了以FPGA为核心器件的视频画面分割的硬件平台,通过硬件形式来实现视频四画面分割,图像的提取、存储等都在一片FPGA内实现,提高了系统的集成度,所有的模块设计都是利用Verilog HDL编程实现,和软件实现方法相比,系统在处理速度方面有了显著的提高。输入/输出的信号都为DVI信号,实现了高清视频画面分割。

fpga相关文章:fpga是什么

评论