一种14位210MSPS校准电流DAC设计

引言

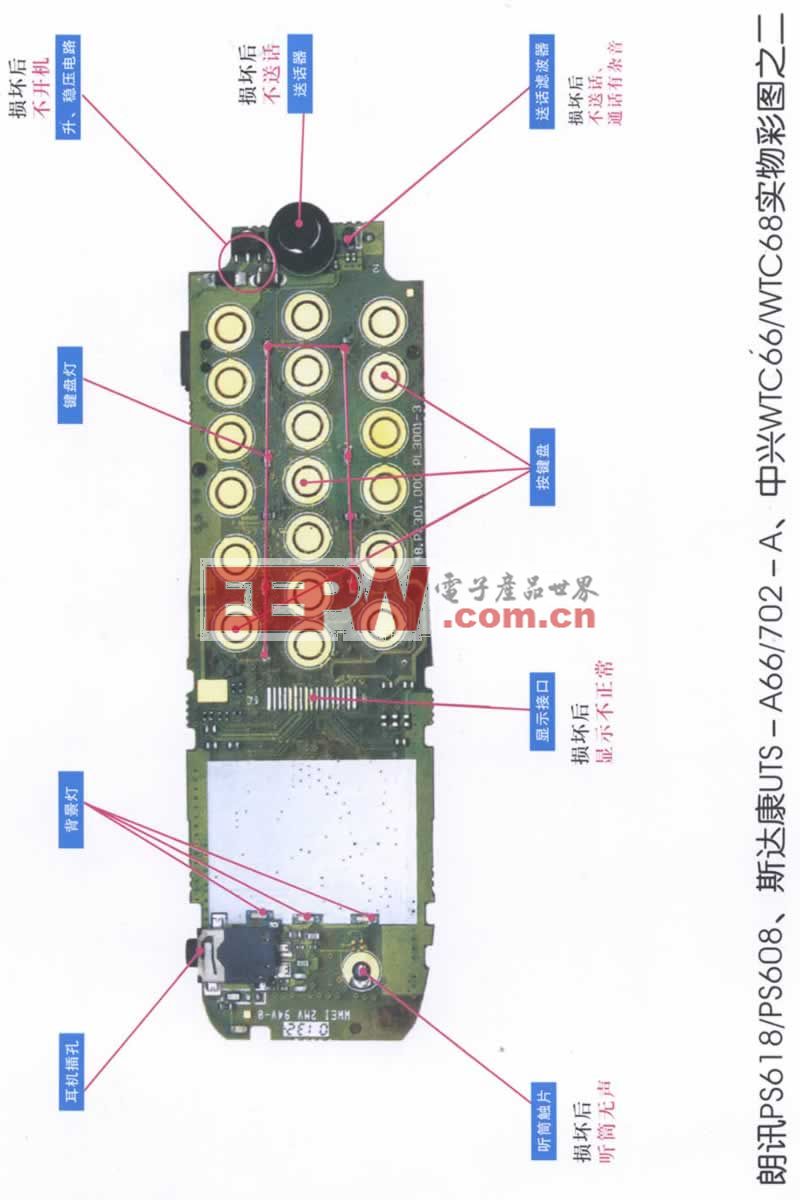

在许多信号处理和无线电通讯设备中,D/A转换器是限制整个系统精度和速度的关键器件[1]。随着CMOS集成电路技术的不断发展和DAC结构的不断创新,现在采用亚微米或深亚微米CMOS工艺可实现高速、高分辨率的DAC。本文介绍了一种采用分段电流舵DAC结构,在保证高速采样的同时,使积分非线性误差(INL)和微分非线性误差(DNL)达到最小化,从而设计完成了一种基于0.35μm CMOS工艺的14位 210MSPS DAC。该转换器采用分段电流沉,在该结构中,5位最高有效位控制31个电流源,4位中间位控制15个电流源,5位最低有效位直接控制二进制权电流源。由于通信系统要求DAC具有高精度的满量程输出电流和良好的动态性能,而输出电流精度主要受带隙电压基准源控制,动态性能则主要受电流转换驱动电路和电流源开关控制,因此本文在分析14位DAC系统结构的同时,也分析了内置的带隙电压基准源、分段电流源开关序列布局和电流开关驱动电路,其中带隙电压基准源可以通过外围管脚实现外部基准电压源截止和取代。最后给出了基于0.35μm 1P3M CMOS工艺的14位DAC的设计仿真和测试结果。

1 DAC转换器结构

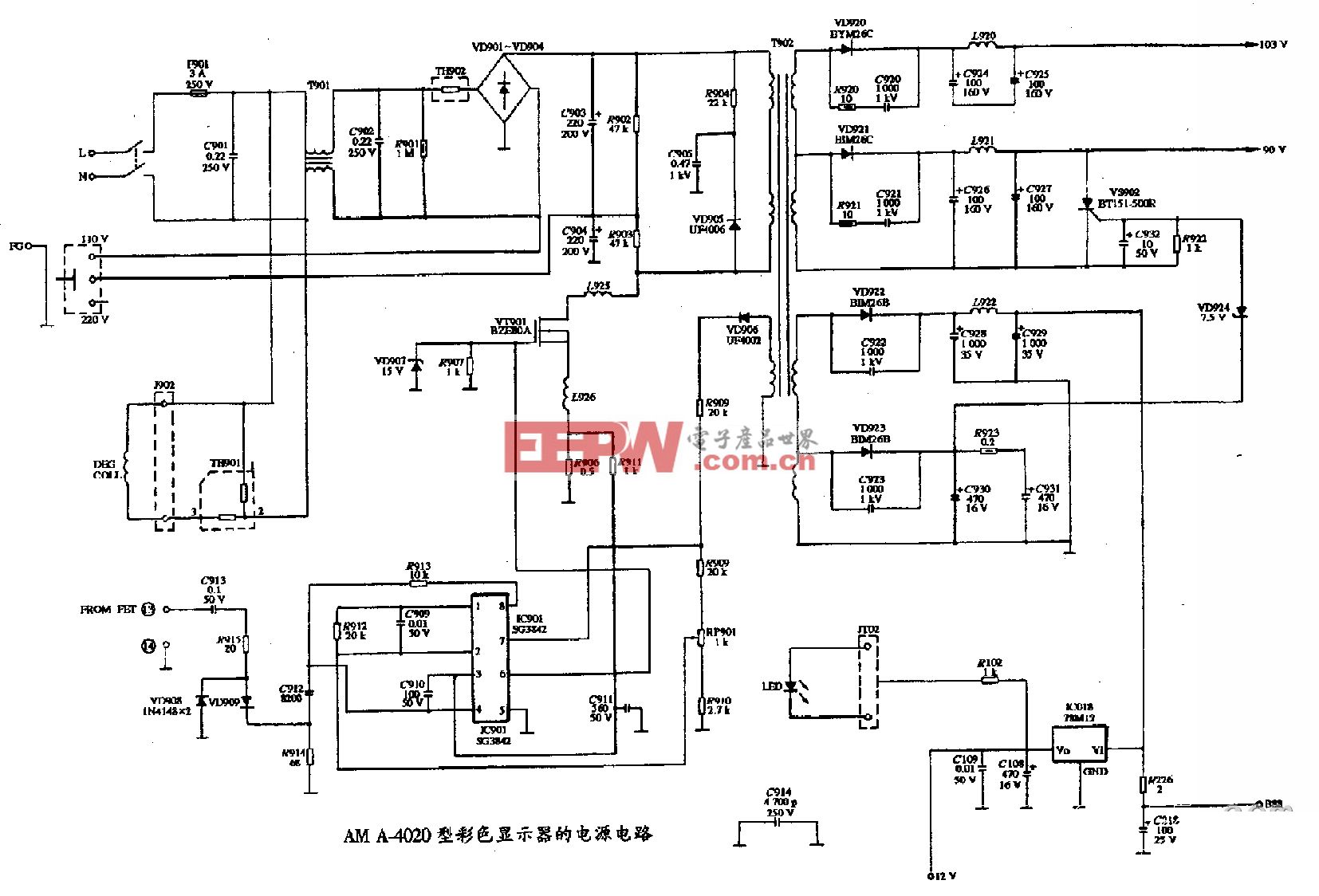

为了达到高速14位精度DAC的要求,一般采用电流沉结构。这是因为根据电子学原理,电流工作模式比电压工作模式快,电源利用效率高。同时考虑到性能和面积的关系,整个转换器采用了5+4+5的分段结构,可以有效减小浪涌引起的性能退化。

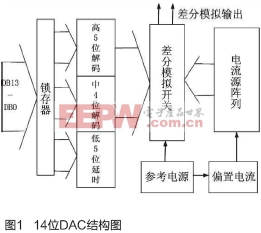

图1给出了14位DAC的结构框图,由参考电源、偏置电路、电流源阵列、高速锁存器、解码电路和差分模拟开关等组成。该电路在工作时,输入的14位数字信号存放在内部寄存器,其中高5位和中间4位经过解码逻辑,把二进制码转变为温度计码,为了保持延时的一致性,低5位则经过伪解码。解码后的数据控制电流源阵列的电流源打开或关断,从而控制电流的增加或减小。本设计内有1.2V参考电压源,以及相应的偏置电路,可以根据需要选择内部参考或外部参考。

2 线性度保证

影响DAC线性度的主要有两种误差来源:随机误差和系统误差。随机误差主要指由于工艺的变化带来的电流源失配引起的误差。我们通过Monte-Carlo仿真工艺变化引起的良率变化,可以确定单位电流源的允许变化范围。根据文献[2]可知,两个单位电流源的标准偏差是偏置电压和沟道尺寸的函数。

是与工艺相关的工艺常数,因而(1)式具有通用性。由式(1)可以看出,采用面积较大的单位电流源可以减小误差。

系统误差主要指由于工艺梯度分布带来的误差。可以采用优化版图、特殊走线方法和优化开关时序减小误差,但不能完全消除。

3 关键电路设计

3.1 参考电源设计

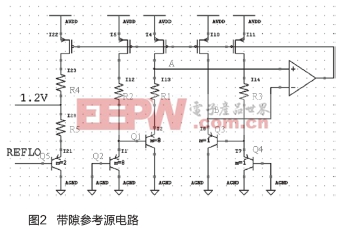

对于高分辨率转换器,参考电源是整个电路的基准,应该特别稳定和精确,与电源、工艺变化关系甚微。现代CMOS工艺中带隙参考基本具备这些条件,因此我们选用带隙参考源。如图2所示。

图2中,Q1、Q2、Q3、Q4和Q5是寄生的衬底PNP三极管,可在标准的CMOS工艺中实现。Q1和Q2,Q3和Q4都以射随器的形式相连,这样可以减小运放失调引起的误差。Q5面积是Q3的2倍,I5、I4、I10和I11是尺寸完全相同的晶体管,I22的宽长比是I4的2倍,它们的栅电压由负反馈运放的输出提供,它们的作用是作为电流源,为各个支路提供偏置电流。电阻R1的作用是使A点和B点的电压产生差值,从而使基准源起作用。电阻R4和R5在PTAT电流之路上,通过它们的分压,产生一个基准电压REFI,REFLO端则是用来控制Q5,使该支路起作用产生REFI的。下面,就通过计算详细地介绍本设计基准源的工作原理。

本设计中,m=8,VEB的温度系数是-1.5~2mV/℃,VT的温度系数是0.085 mV/℃,所以,为了让上式等于0,本设计取R5/R1为2.12~2.83。

本设计中的带隙基准源经过调整,在室温下的输出为1.207V。

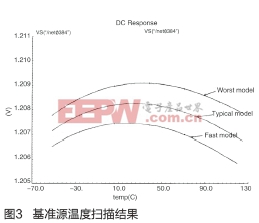

图3示出了用spectre仿真器对基准源在-55℃-125℃的范围内进行温度扫描的结果,如图3。

从图3可以看出,带隙电压的温度相关性曲线是一条抛物线的形状,在室温时,该曲线达到顶点,这很符合设计要求。从图3我们可以算出电压基准源的温度系数为15ppm/℃。

3.2 高速电流开关及开关信号设计

电流开关设计的关键参数是导通电阻和时钟馈通。为了减小开关上的电压降对电流源线性度的影响,开关的导通电阻必须很小。对时钟馈通,我们采用了差分反向抵消技术和沟道电荷吸收技术,可以有效地减小信号馈通引起的失真。另外,我们采用了摆幅限制电路来提高电路工作的速度。

开关信号的设计对D/A转换器的性能也有比较大的影响,对高速高性能应用,必须保证开关信号的驱动电路足够快和精确,而且要尽量减小抖动和浪涌的产生,必须认真进行设计。

本设计中电流开关包括电流开关驱动电路和电流控制开关两部分。电流开关驱动电路产生用于控制电流开关的信号,因此是对DAC的动态性能影响最大的电路模块之一。电流开关驱动电路的前级电路是同步锁存器,电流开关驱动电路根据同步锁存器的互补输出信号驱动电流开关。电流开关驱动电路对输入信号进行缓冲,并为电流开关提供尽可能好的控制信号。开关信号的设计对D/A转换器的性能也有比较大的影响。因为我们是对电流源进行开关,必须保证电流开关不能完全关断,否则在关断时会使电流源输出电压飘向电源电压;而当开关打开时,由于电流源两端的电势差不能突变,否则会引入较大的浪涌。极端情况下,电流源的晶体管可能进入线性区,使输出阻抗变糟。为了避免这种情况发生,我们采用差分开关结构,这样就始终存在电流通路。开关信号应保持完全匹配,使浪涌降低到最小程度。另外,应保持开关信号的上升时间和下降时间尽可能相等。

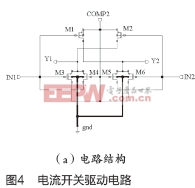

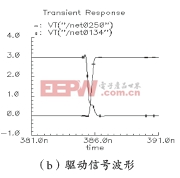

电流开关驱动电路及其仿真结果波形如图4所示。

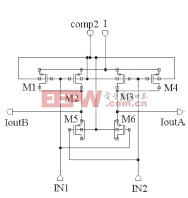

在本设计中,电流开关是PMOS管差分对的结构,并设计在同一N阱中,从而较好地避免了开关噪声和浪涌能量等不利影响。同时为了降低时钟馈通的影响,我们加入了冗余晶体管结构。电流开关电路结构如图5所示。

图5中的电流开关由6个PMOS管组成,M1和M2并联,M3和M4并联,他们构成了一对差分开关,而M5和M6是冗余晶体管。信号IN1与IN2是上级电路——电流开关驱动电路输出的互补开关控制信号,由于他们的高电平是comp2,所以本电路中晶体管的衬底都接comp2,这样就能够降低偏衬效应引起的噪声。

3.3 电流调整电路

本设计可以通过熔丝编程技术,对高中低位的电流进行调整,从而降低芯片的INL、DNL和增益误差,使芯片的性能得以提高。对电流的调整需要控制成比例电流的添加或抽取,但是此控制要通过电流源开关实现,控制这些开关的就是熔断丝电路阵列。在编程熔断状态下,通过编程来熔断相应的熔断丝,以使该熔断丝电路控制的电流源开关处于常开状态,从而实现对芯片线性度的永久修正。编程端口对熔断丝阵列的控制是通过行列译码器实现的。

4 测试结果

通过电路和版图优化设计,以及采用校准技术,转换器性能有了较大提高。表1给出了采用0.35μm 1P3M CMOS工艺得到的样片电路测试结果。在输出5.04MHz(@SPAN 4MHz)时,其SFDR为84.9dB。

参考文献:

[1]Yang C,et al.A serical-link transceiver based on 8-G samples/s A/D and D/A converters in 0.25-μm CMOS.IEEE J.Solid-State Circuits,2001,36(NOV): 293-301

[2]Bastos J,et al.A High Yield 12-bit 250-MS/s CMOS D/A converter.IEEE custom integrated circuit conference.1997:431-434

[3]孔瀛,王宗民,许军.一种16位高速数模转换器(DAC)的设计与实现. 电子产品世界,2014(1):71-73

[4]张倬,王宗民,周亮,等.低功耗8-bit 200MSPS时间交织流水线ADC.电子产品世界,2013(12):71-73

[5]蔡伟,杨松,谭博.8位1.0GSPS ADC芯片MXT2001原理与应用.电子产品世界,2013(11):62-63

手机电池相关文章:手机电池修复

评论