谈谈旁路和去耦合电容-原理部分

看了很多关于旁路电容和去藕电容的文章,有代表性的如下:

退耦电容的选择和应用

十说电容

关于旁路电容和耦合电容

关于旁路电容的深度对话

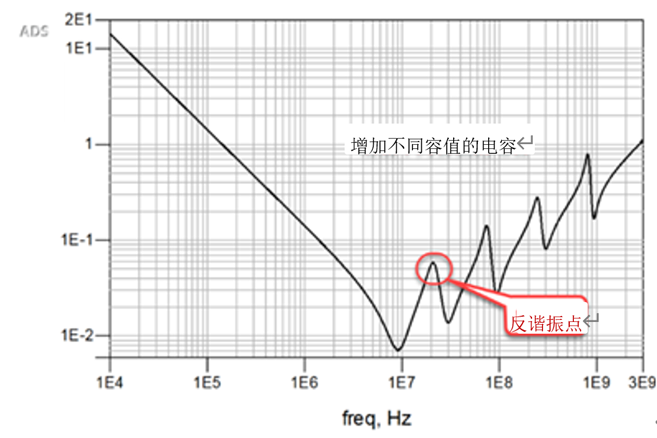

对于以上的文章,我是很佩服的,我按照它们的思路把问题推演和考证了一下,参考了一些数据,自己推导一下电容模型的阻抗曲线,试图做的就是让问题更明显一些。打算把这个问题分成两个部分,第一个就是原理上去验证,第二个就是从实际的例子去推演。各位看完有任何意见请留言。

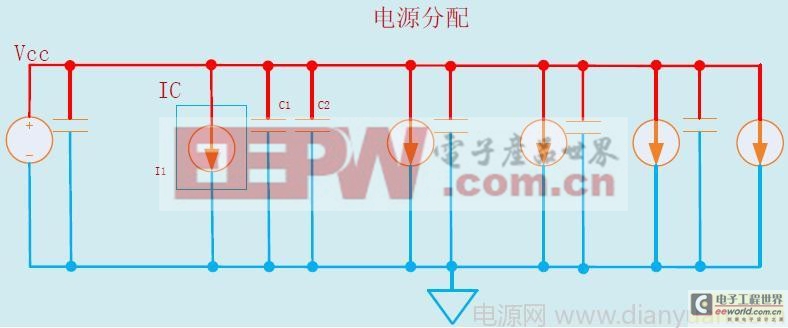

先看看此类电容的应用场合:

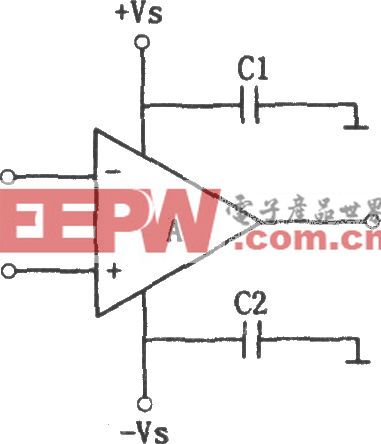

根据以上电路来说,由一个电源驱动多个负载,如果没有加任何电容,每个负载的电流波动会直接影响某段导线上的电压。

瞬间冲击电流的产生原因

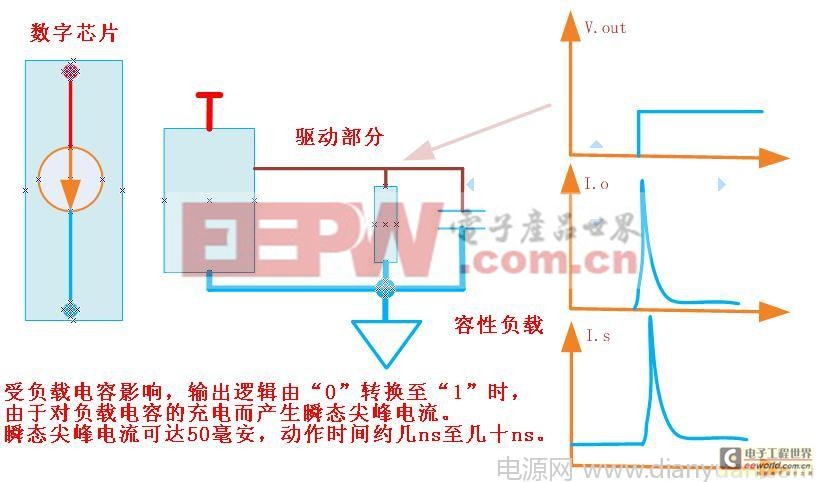

1.容性负载

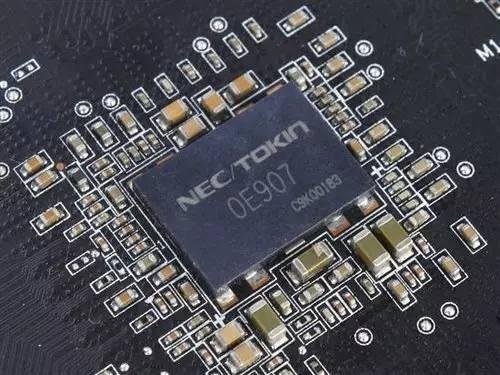

来分析一下数字电路的电流波动,数字电路的负载并不是纯阻性的,如果负载电容比较大,数字电路驱动部分要把负载电容充电、放电,才能完成信号的跳变,在信号上升沿比较陡峭的时候,电流比较大,对于数字芯片来说,新派驱动部分电流会从电源线上吸收很大的电流,由于线路存在着的电感,电阻(特别是芯片管脚上的电感,会产生反弹),这种电流相对于正常情况来说实际上就是一种噪声,会影响前级的正常工作,下图反应了工作情况

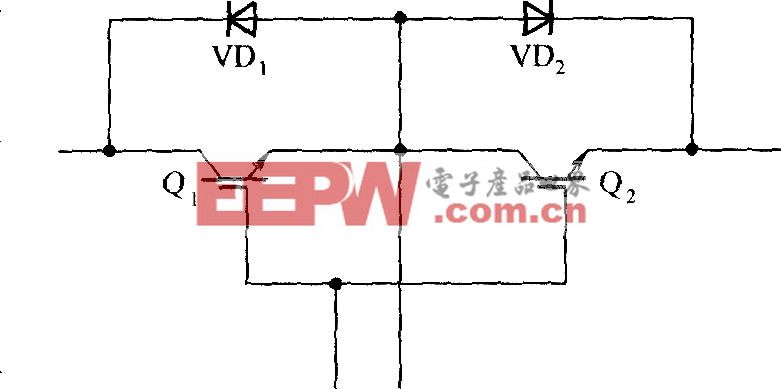

2.输出级控制正负逻辑输出的管子短时间同时导通,产生瞬态尖峰电流

PMOS和NMOS同时导通的时候出现的电流尖峰。

电压塌陷噪声

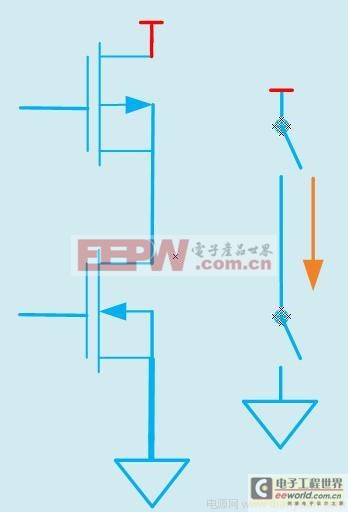

我们考虑数字电路内部结构一般由两个Mos管组成,为了便于分析,我们假设初始时刻传输线上各点的电压和电流均为零。现在我们分析数字器件某时刻输出从低电平转变为高电平,这时候器件就需要从电源管脚吸收电流(上面一个分析的是容性负载,现在考虑的是阻性负载)。

从低到高(L=>H)

在时间点T1,高边的PMOS管导通,电流从PCB板上流入芯片的VCC管脚,流经封装电感L.vcc,通过PMOS管和负载电阻最后通过返回路径。电流在传输线网络上持续一个完整的返回时间,在时间点T2结束。之后整个传输线处于电荷充满状态,不需要额外流入电流来维持。

当电流瞬间涌过L.vcc时,将在芯片内部电源和PCB板上产生一个电压被拉低的扰动。该扰动在电源中被称之为同步开关噪声(SSN)或Delta I噪声。

从高到低(L=>H)

在时间点T3,我们首先关闭PMOS管(不会导致脉冲噪声,PMOS管一直处于导通状态且没有电流流过的)。同时我们打开NMOS管,这时传输线、地平面、L.gnd以及NMOS管形成一回路,有瞬间电流流过开关NMOS管,这样芯片内部至PCB地节点前处产生参考电平被抬高的扰动。该扰动在电源系统中被称之为地弹噪声(Ground Bounce)。

实际电源系统中存在芯片引脚、PCB走线、电源层、底层等任何互连线都存在一定电感值,就整个电源分布系统来说来说,这就是所谓的电源电压塌陷噪声。

电荷放大器相关文章:电荷放大器原理 电容相关文章:电容原理 电子负载相关文章:电子负载原理

评论