使用事件系统和DMA来消除中断可实现超快响应时间和极低功耗

随着嵌入式系统与外围环境的响应越来越多,需要捕获和处理数据的外设数量也暴增。微控制器通常配备ADC、DAC、PWM、多个定时器/计数器,以及大量的TWI、SPI、CAN、USB和USART通信接口。外设的增加意味着需要循环密集(cycle-intensive)的中断,而在内存和外设之间移动的数据量也会呈指数级增加。

一般来说,CPU负责处理中断和移动数据。在某些应用中,CPU的大多数时间都花费在这些活动上。例如,管理两个同步外设之间的通信和64Mbps速率的单一数据传输就需要200 CPU MIPS,并消耗240mA电流,原因是这涉及了广泛的场景关联转换和中断处理。要应对这些额外的计算负荷,就必须提高CPU时钟速率,因而相应地增加了功耗。在极端情况下,还必须把设计从8/16位器件转换成32位器件才能应付。

在多数情况下,一个外设上的信号除了要让另一个外设知道它有事要做外,并不需要CPU做什么。可惜的是,两个外设间的联络却需要大量中断处理时间。例如,在马达控制应用中,为防止马达过热,必须不断测量马达上的电流,并在出现过流马达停转信号时触发一个模拟比较器。这样CPU便会随之中断,并关断马达驱动电路的PWM输出。这个过程需要耗费数十个时钟周期,并需要另外的20~100个时钟周期来恢复关联。微控制器并没真正被用于任何需要其处理能力的事情,只是从模拟比较器向PWM输出传递了一个消息而已;换言之CPU时钟资源基本上被浪费了。

除此之外,定时器/计数器为其它外设(ADC和DAC)的定时也会耗费CPU时钟的资源。在这类情况下,都要产生一个中断来开始一次转换。在几个kHz的抽样速率下,这些定时器/计数器中断会消耗掉1MIPS,大约是一个12MIPS CPU的8%的处理能力。

如果这些外设能够无需中断CPU而直接相互通信,每秒钟就可轻易节省数百万个时钟周期。8位微控制器不再适用于8位应用的一个原因,就是应用涉及的数据处理和中断处理太多,CPU的MIPS大都耗费在这些活动上。而外设和内存之间的传输数据更进一步地增加了MCU的负担。一个350kps的数据传输就要耗费22~25个CPU MIPS。

解决这个问题的一个方法是采用一个带8通道事件系统和直接内存访问(DMA)的低功耗8/16位单周期RISC MCU,让事件系统和DMA来为CPU分担这些工作。这种微控制器构架可同时处理多达8个外设间事件,以及4个速率为64Mps的数据传输,而且总体电流消耗低于10mA。由于事件系统和DMA可让外设自主地相互通信,因此不再需要CPU时钟周期或中断,这样CPU也就可以处于睡眠状态了。

事件系统通过CPU数据总线和DMA控制器之外的一个专用网络传递外设信号。这样做的好处是外设间信号通信变得可预见和无延迟,并减少了CPU时间和释放了中断资源。有了事件系统,当一个外设出现了状态变化,就会自动触发其它外设上的相应动作。在前述马达案例中,微控制器中的模拟比较器、定时器/计数器,I/O引脚或ADC可以在过流状况的两个时钟周期内,直接关断马达驱动电路的PWM输出,不需占用任何中断,也不耗费任何CPU时钟资源,就可以为马达提供更好的保护。

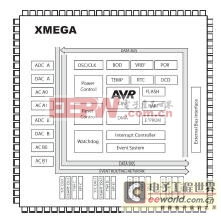

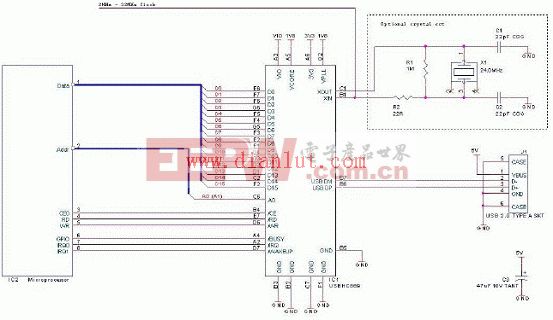

图1,带有事件系统总线的XMEGA微控制器:带有事件系统和DMA的MCU通过CPU数据总线和DMA之外的一个专用网络传递外设信号。这样做的好处是外设间信号通信变成可预见和无延迟,并减少了CPU周期时间和释放了中断资源。

图1,带有事件系统总线的XMEGA微控制器。

可以触发事件系统的外设事件包括:定时器/计数器比较匹配或溢出,模拟比较器触发,引脚状态变化,ADC完成或比较,以及实时计数器溢出。在其它外设中被触发的事件包括:ADC或 DAC转换,输入捕获以记录通信时间戳或ADC测量时间戳,外部频率或脉宽测量,产生定时器/计数器时钟信号,开始一个DMA交易,或改变一个引脚输出。

至于哪些事件应该触发特定外设上的哪些动作,完全可由设计人员进行配置。事件系统配置可以是静态锁定的,也可在应用执行的不同阶段动态变化。事件通道并行运作,任何时刻都可有多达8对外设同时互联。

采用事件系统能够消除多个和/或频繁的中断触发造成的瓶颈,而且无需软件开销,关键任务可独立于CPU完成,而且也能大大降低功耗。一个没有事件系统的传统8位MCU要耗费16 MIPS才能完成响应马达过流信号关断PWM的动作。在16 MHz,1 MIPS/MHz,以及0.6 mA/MHz的工作条件下,微控制器需要消耗8.6 mA才能完成这项任务。而一个带有事件系统的同等MCU则不消耗MIPS,而且也不会增加功耗。

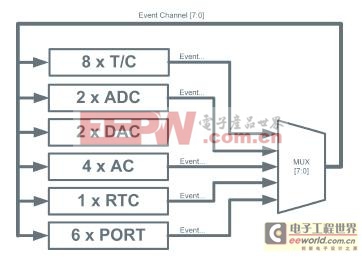

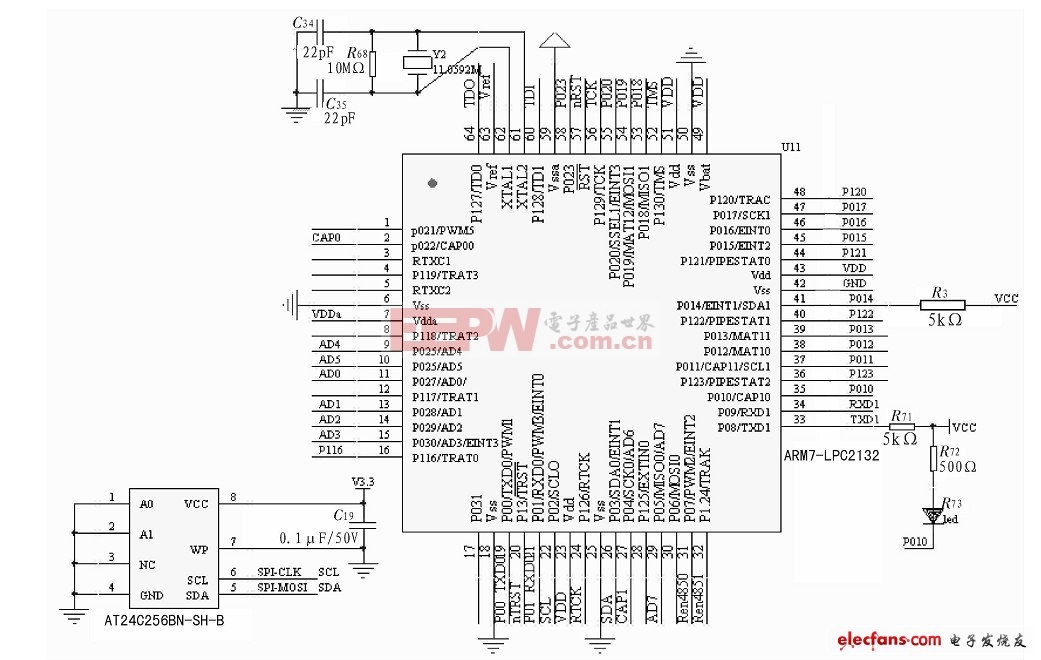

图2,XMEGA微控制器的事件系统:有了事件系统,一个外设上出现状态变化就会自动触发其它外设上的相应动作,且不 占用任何中断,也不耗费任何CPU时钟资源。可同时处理多达8个外设间事件,以及4个速率为64Mps的数据传输,而CPU处于睡眠模式,电流消耗仅10mA。

图2,XMEGA微控制器的事件系统。

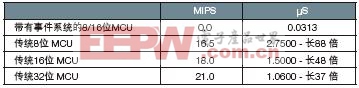

消除中断后,处理响应延迟可获减少,而且确保最多只要2个时钟周期,或者说在32 MHz 时钟频率下只需62.5 ns的时间;而最快响应时间可达到31.2 ns。实际上,在8/16位MCU上采用事件系统,响应时间较无事件系统的传统32位MCU 缩短了37倍。

传输数据是另一个耗费时钟周期和增加功耗的活动。由于CPU本身每次只能传输1个位,因此用CPU传输数据会带来巨大处理开销很大。8位微控制器必须执行22 MIPS,消耗14mA电流才能完成速率350Kbps的数据传输。SPI和USART传输的数据速率高达25Mbps,普通的8位MCU几乎不可能支持这个最大速率。

只要在器件上增加一个外设DMA控制器,就可基本上解除CPU的所有这些工作负荷。当CPU数据总线空闲时,DMA控制器便会用它来完成内存和外设间的数据传输,无需使用CPU资源。连接外设寄存器的内部总线(包括I/O引脚、内存映射EEPROM、内部SRAM,以及外部总线接口)是分开的,因而DMA控制器和CPU可以同时进行总线访问。这样,始终有一个通信通道供DMA使用。

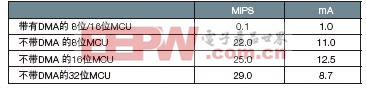

跟处理能力为22 MIPS、功耗为11mA但不带DMA的8位MCU比较,使用DMA控制器传输350 Kbps数据,MIPS消耗可减少99%;电流消耗则低于1mA。

DMA控制器可以直接将数据从一个外设寄存器移到内部或外部SRAM,也可在SRAM的不同地址间,甚至不同外设寄存器之间移动数据。4个DMA通道有着各自的优先级、来源、目的地、触发方式、寻址模式,以及传输块大小。由于RISC CPU中简单的线性内存地址空间以及DMA控制器的自动增/减和重新加载的特点,DMA一次可传送1到16M字节。

若事件系统与DMA控制器配合使用,就可按如下方式完成模数和数模转换:任何I/O引脚上的状态变化或任何定时器/计数器出现溢出,就会触发ADC转换,无需任何CPU开销。ADC转换结果通过一个DMA通道传送到SRAM。同时,第二个定时器/计数器会触发一个高速DAC转换,并用第二个DMA通道传输相应的数据。事件系统会让模拟比较器触发输入捕捉,以100%精度记录时间戳,触发自动捕获,记录通信交易的起始时间戳,或在第二个ADC上扫描ADC转换。4个事件通道仍是可使用的,它们可用于PWM输出的故障保护,控制一个高压驱动级、定时器/计数器的级联,以及两个通信通道,所有动作均在同时进行,而CPU则处于睡眠状态。

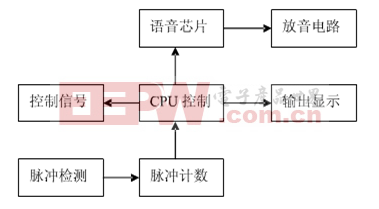

图3,XMEGA的事件处理:若事件系统与DMA控制器配合使用,就可按如下方式完成模数和数模转换:任何I/O引脚上的状态变化或任何定时器/计数器出现溢出,就会触发ADC转换,无需任何CPU开销。ADC转换结果通过一个DMA通道传送到SRAM。

图3,XMEGA的事件处理

在微控制器中增加事件系统和DMA对功耗有很大改善。在某些应用中,这样做可使MCU在大多数时间都处于睡眠模式,功率消耗仅80 uA/MHz,而所有的外设却仍继续工作。对一个有8个同时事件和4个350 Kbps数据传输的应用而言,一个带有事件系统和DMA的8/16位MCU,每秒将有3160万个周期处于睡眠模式,而总电流消耗仅4mA。任何不带事件系统和DMA的8/16位MCU则会消耗52 至 60 mA的电流。而一个32位MCU则会消耗34.8 mA的电流,几乎是带有事件系统和DMA处理器的10倍功耗。在一个中断频繁和数据量大的应用中,带有事件处理器和DMA的微控制器可节省90%的功耗。

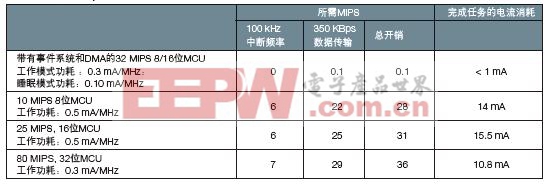

有/无事件系统和DMA之MCU的处理周期和功耗比较见表3。

表1,有/无事件系统之MCU的处理周期和响应时间比较

表2,有/无DMA的MCU传输350 KBps数据时的典型MIPS和功耗

表3,传输350Kbps 数据的中断、MIPS和功耗比较

比较器相关文章:比较器工作原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论