Alpha MOS在PFC应用中的注意事项与设计要点

3 Alpha MOS的并联及PCB设计

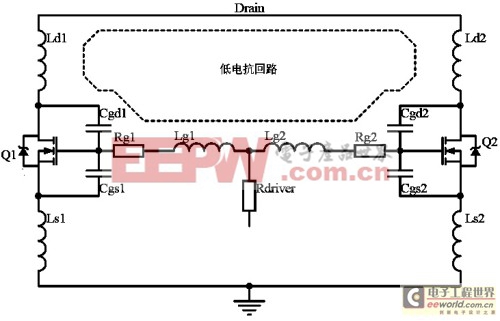

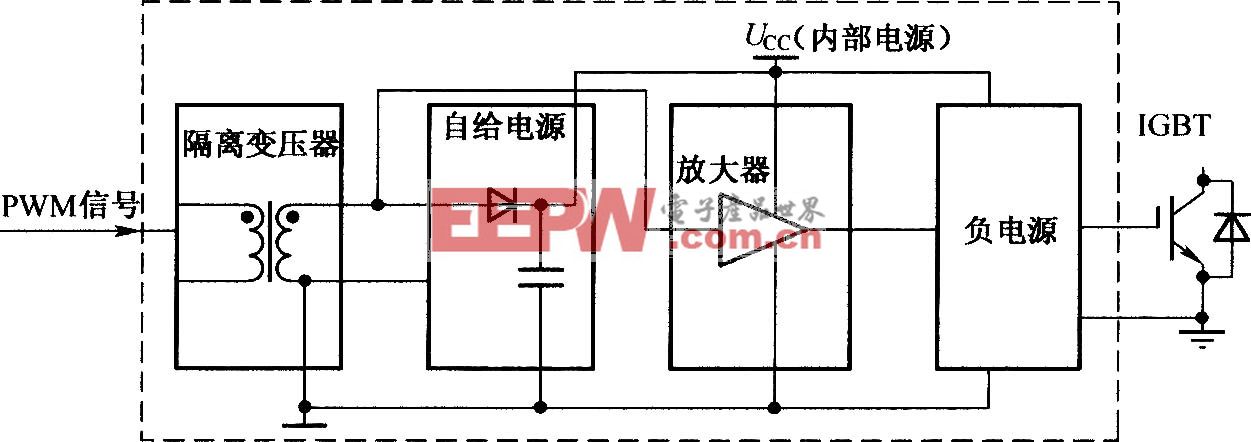

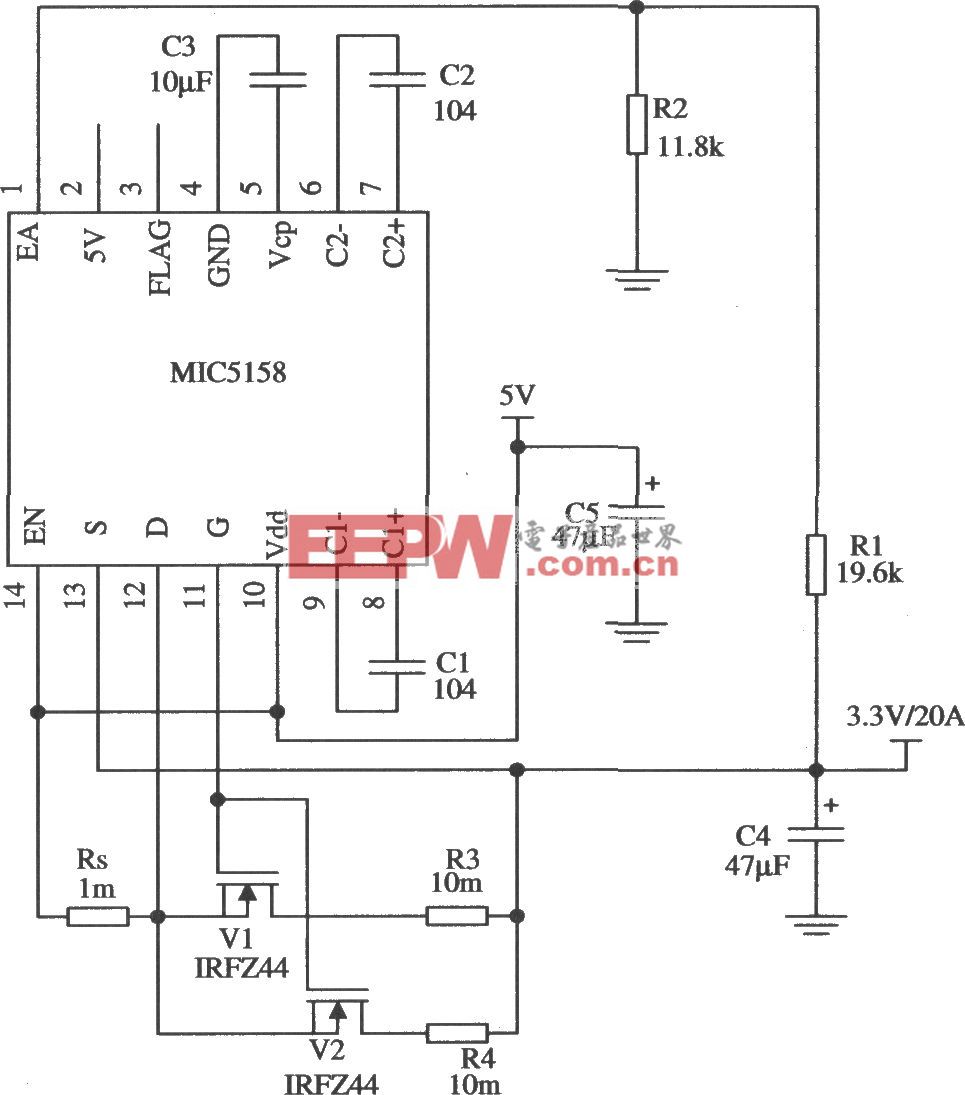

对于MOS并联的情况,首先驱动电路要尽可能隔离。严禁直接将并联MOS的驱动端连在一起。由于MOS的漏极电感,结电容以及门槛电压等可能有差异,直接将门极相连会使门极驱动在开关过程产生振荡,如图13所示,振荡将在低电抗回路中发生,严重时会导致MOS损坏。驱动电阻增大可以对并联振荡起到衰减作用,最好严格地隔离并联驱动。

图13:直接并联的驱动干扰模型

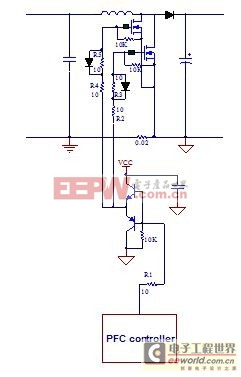

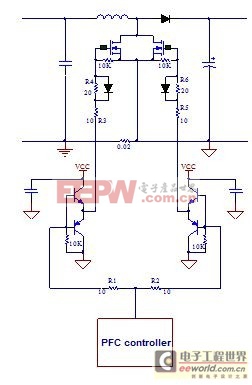

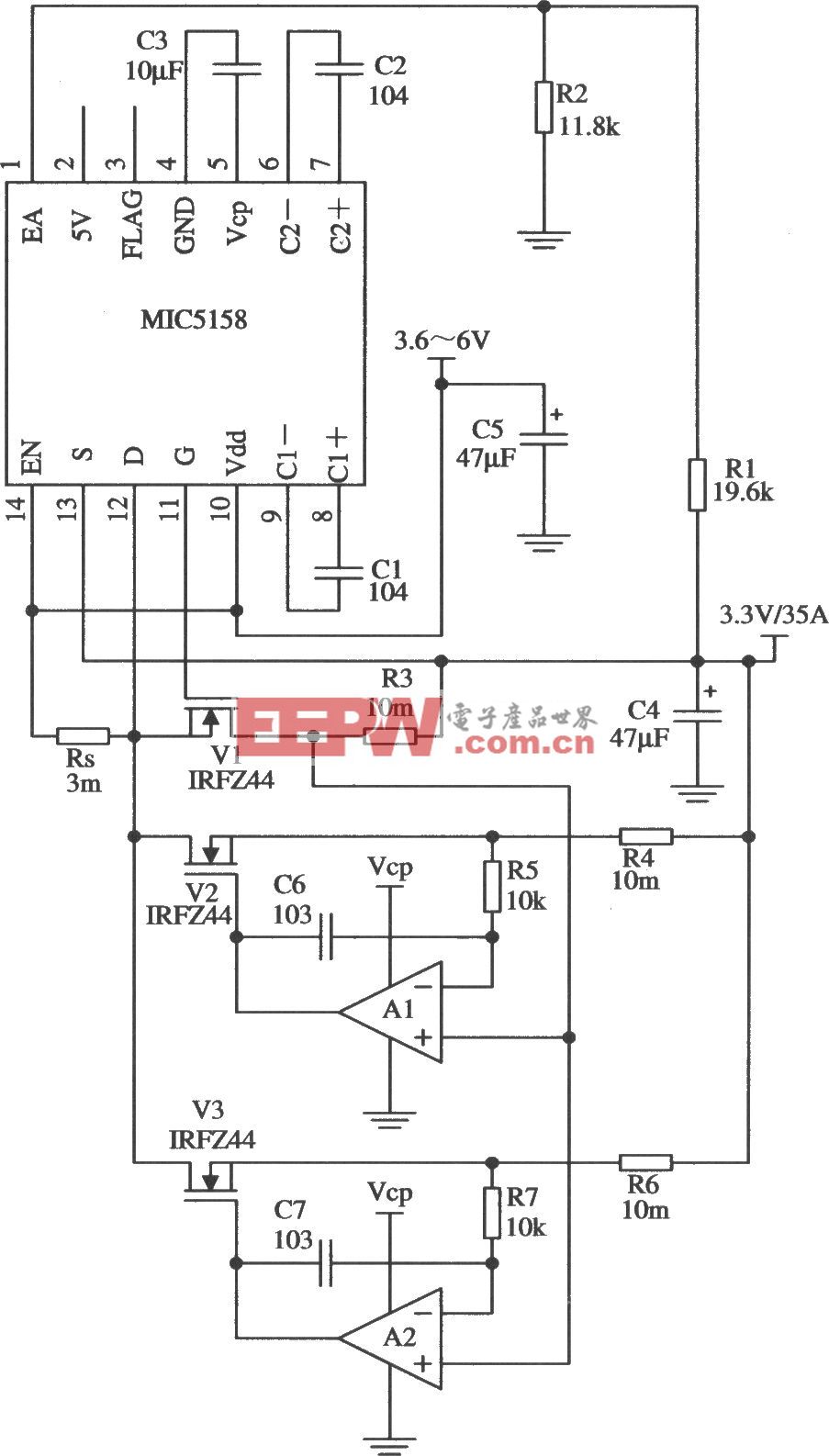

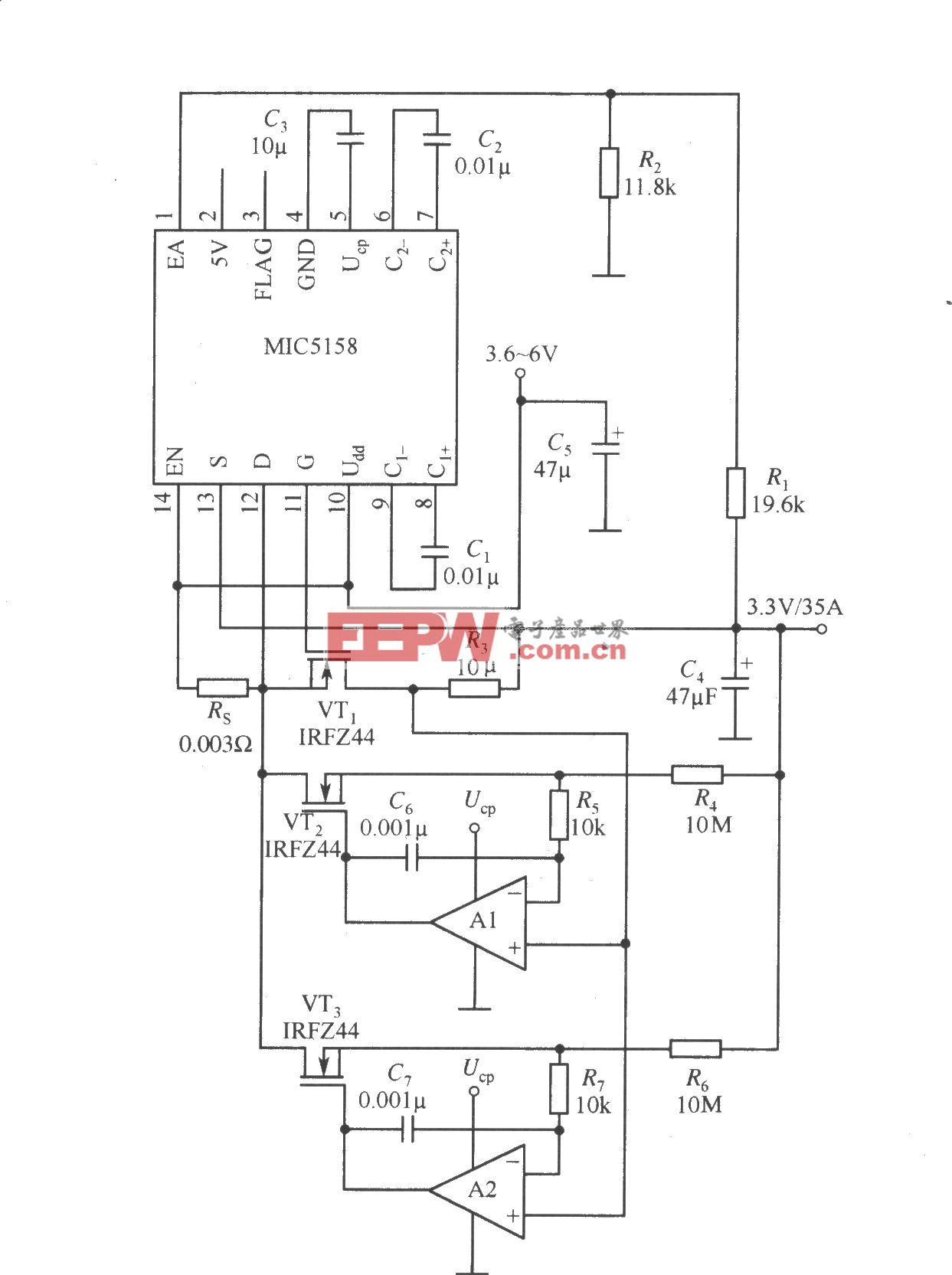

图14所示为常见的并联方式,并联的MOS分别通过驱动电阻与图腾柱电路相连。但这种隔离还不够彻底,彻底隔离的方式如图15电路所示,两个MOS分别经过各自独立的驱动电路驱动,只在信号输出端相连。不管采用哪种驱动方式,为了提高可靠性,增大驱动电阻,降低dv/dt(比单管更低)都是必要的。

需要说明的是,在并联应用中,驱动受干扰的问题要优先于并联的不平衡问题。一般的电路中很难保证并联的绝对平衡。如果驱动电路和PCB布局不能兼顾的情况下,可以适当牺牲一些平衡性,但驱动的干扰必须被消除。具体应用中需要仔细权衡。

图14:常用并联驱动电路

图15:完全隔离并联驱动电路

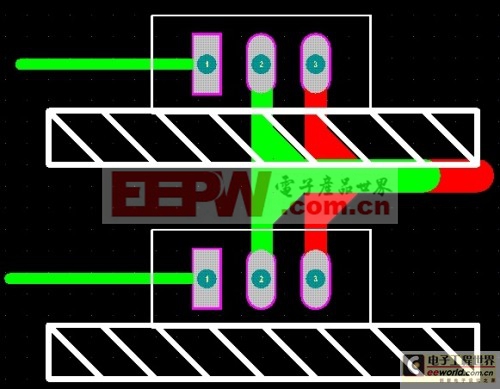

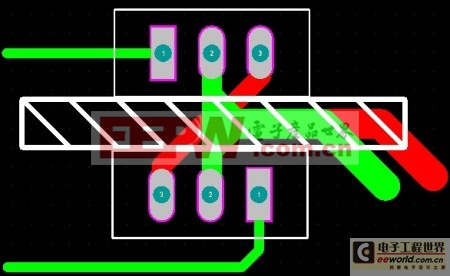

并联中PCB布局和走线十分重要,越是高速开关的MOS,对并联均衡的要求就越高。不均衡的并联,不但会导致单个MOS承受过高的电流冲击和dv/dt(注意到dv/dt与电流成正比)还会在电流重分配的过程中产生振荡,干扰驱动和其他信号。下面是一些MOSFET并联的例子,绿色为正面走线,红色为背面走线。

图16和图17是最佳的并联走线方式,并联的MOS各自漏极和源级的走线长度相同,驱动走线与主功率走线在不同方向。实际应用中可以增大走线面积以取得更好的效果。

图16:并联MOS散热片独立

图17:并联MOS散热片共用(背靠背)

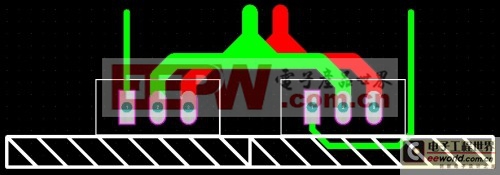

图18的MOS布局方式在一些中小功率应用中比较常见,采用这种走线方式可以取得均衡的效果,但是实际应用要注意减少走线长度以减小走线电感。

图18:并联MOS散热片共用(并排)

图19是一种不良走线方式,左边的MOS上串联了一段走线电阻和电感,这可能导致右边MOS的工作电流更大,dv/dt和di/dt也更大

图19:并联MOS散热片共用(并排),不良走线

在一些中小功率的实际应用中,PCB是单面板,常常采用图20的方式并联。虽然这种方式仍然不能实现走线电感的均衡,但是通过走线露铜涂锡,减少了电阻的不平衡。

图20:并联MOS散热片共用(并排),单面板小功率

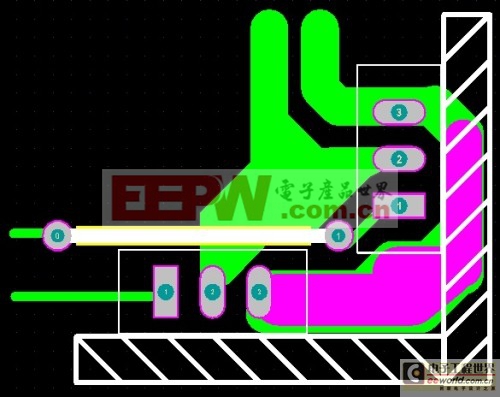

图16和图17的布局方式不是很容易实现,图21是单面板PCB,并联MOS在散热片拐角处放置,通过增加走线面积和露铜等方式,可以在一定程度上减少不均衡问题。

图21:并联MOS散热片直角布局,单面板

总结

Alpha MOS是AOS新一代高压MOSFET产品,它具有导通电阻小,开关速度快,结电容小的特点。Alpha MOS在PFC的应用需要特别谨慎,尽量通过增大Rg,增加Cgs等方法控制dv/dt小于20V/ns,并控制启动过程抑制冲击电流。由于Alpha MOS的高速开关特性,需要注意驱动电路设计和PCB版布局,尽量减少干扰,在并联应用中也需要采用独立的驱动电路和合理的PCB走线。

评论