Alpha MOS在PFC应用中的注意事项与设计要点

Super-junction类型的高压功率MOSFET具有更低的导通电阻,因此在通信电源,服务器电源,电源适配器以及台式电脑电源和照明整流器等应用中得到广泛的使用。Alpha MOS就是基于Super-junction技术开发的高压功率MOSFET,其采用8英寸晶圆,明显提升了器件性能和可靠性。

本文主要针对Alpha MOS在主动功率因素校正电路(PFC)中的设计要点和注意事项给出建议和解决方案。

1.Alpha MOS的工作特性

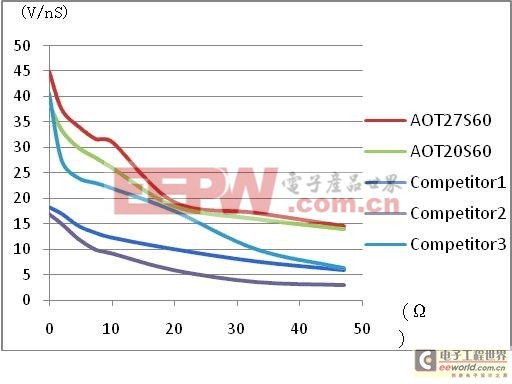

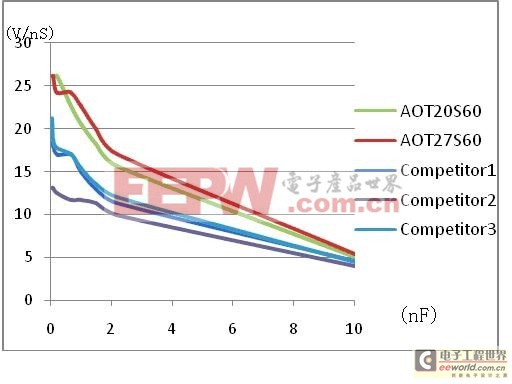

Alpha MOS的导通电阻x芯片面积(RdsA)性能指标比AOS平面工艺MOSFET高3.5倍,导通电阻x米勒电容(RdsxQgd)性能比平面工艺MOSFET高5.7倍。Alpha MOS是目前super-junction产品中同等级下FOM性能最高的,比同等级排名第二的高速开关型super-junction 产品高出45%(图1)。

图1:RdsxQgd和FOM(RdsxQg)的性能对比

由于Alpha MOS 具有开关速度快,结电容小的特点,对减少开关损耗,提高效率有很大帮助。但是在设计中需要更谨慎小心。与传统的MOSFET相比,Alpha MOS需要更仔细的设计驱动电路和PCB布线,在并联应用中也需要格外注意开关噪声对驱动信号的影响。

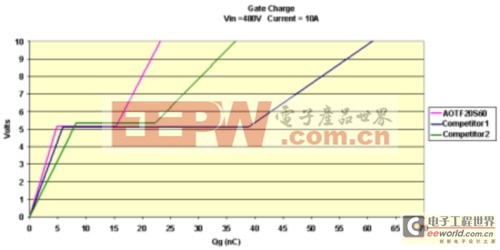

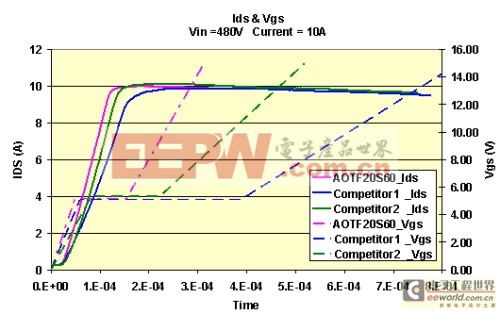

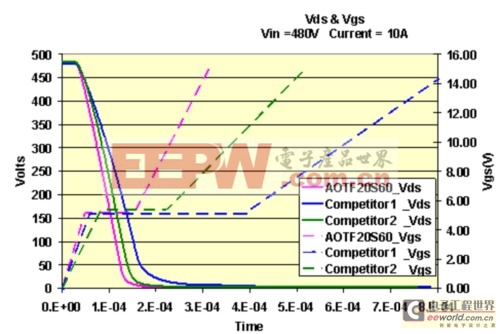

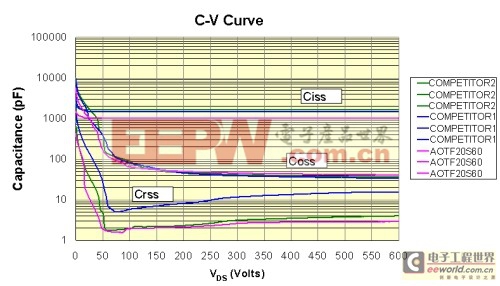

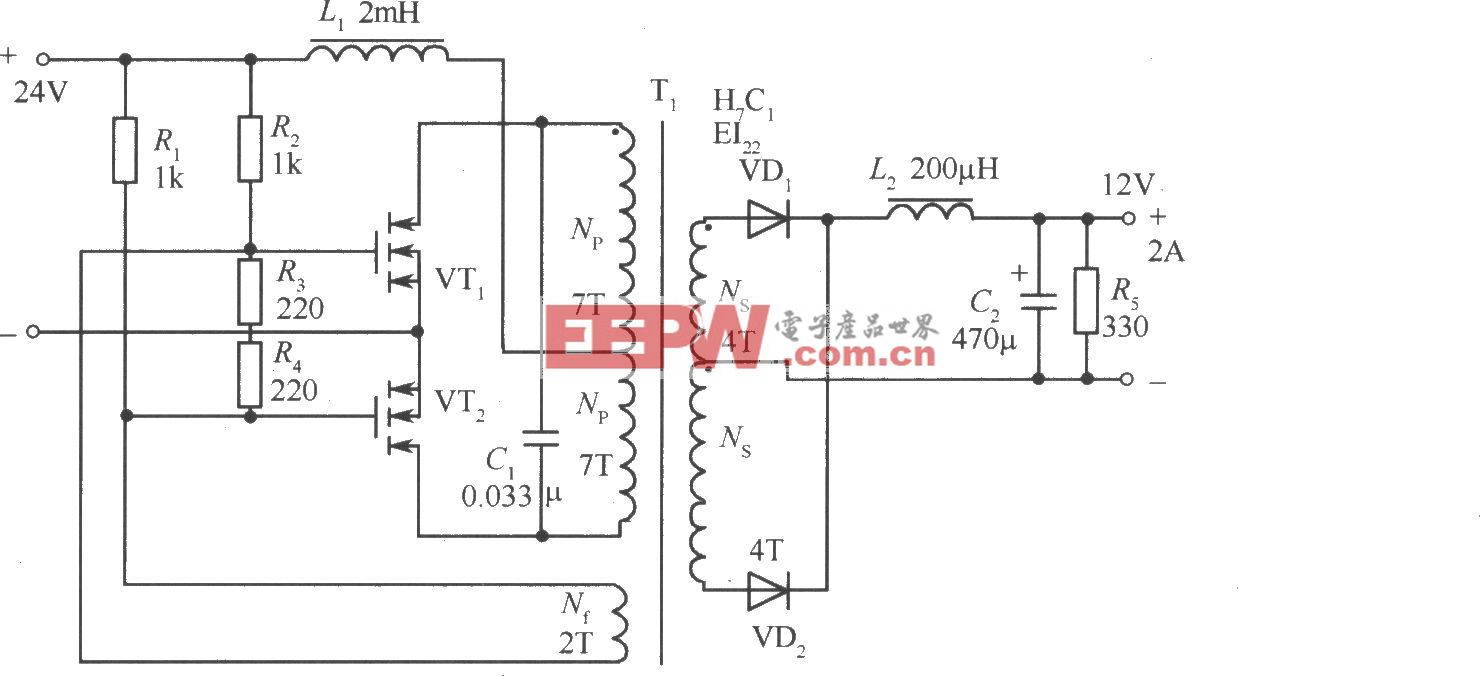

Super-junction类型的MOSFET由于其特有的空间电荷结构,开关速度比传统MOSFET快的多。图2-图5是600V/20A等级super-junction 产品的开关特性对比。competitor1为电源类产品应用最广泛的一种super-junction型 MOSFET,competitor2则是另一种高速开关型的super-junction MOSFET。

图2:门极驱动电荷对比

图3:漏极电流与门极驱动关系对比

图4:漏极电压与门极驱动关系对比

图5:结电容与漏极电压关系对比

从对比中可以看出Alpha MOS主要的优势在结电容,同等级的MOSFET结电容越小,在同样驱动条件下开关速度就越快,在硬开关电路中,这是一个很大的优势。但是过快的开关速度会产生很高的dv/dt和di/dt,这对于MOS的工作可靠性是有害的,同时也是电源系统中噪声的来源。

Alpha MOS的Qg很小,对于减少驱动损耗是个优点。在实际应用中,Qg或者Ciss小的MOSFET,它的驱动信号更容易受主功率回路的干扰,特别在高压应用中这个问题十分突出。如果对开关速度不加限制,过高的dv/dt 很容易耦合到驱动回路中,造成驱动信号紊乱,甚至导致MOS烧毁。

在大功率应用中,MOS的并联往往是常用的手段。但是对于像Alpha MOS这样的高速开关器件,并联需要格外注意。开关速度越快的MOS,并联时越容易导致工作不平衡,驱动参数选择不当甚至会导致额外的干扰。

可以看出,Alpha MOS虽然性能优异但是对设计使用的要求也比较高。它并非如传统的开关器件可以“拿来就用”。选择合适的拓扑,仔细调节驱动参数,合理规划PCB布局,都有助于增加电路的稳定性,避免不必要的重复劳动。

2.Alpha MOS驱动电路设计

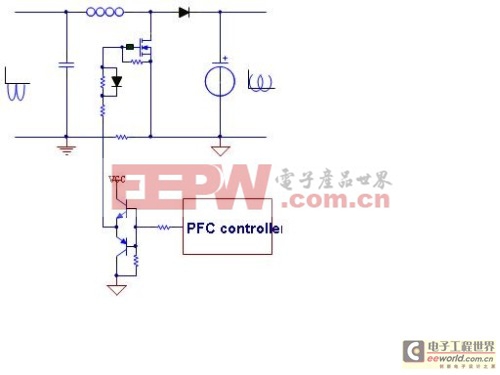

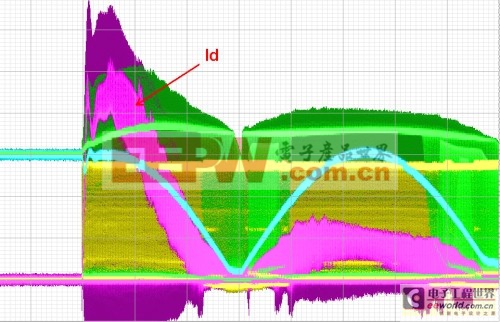

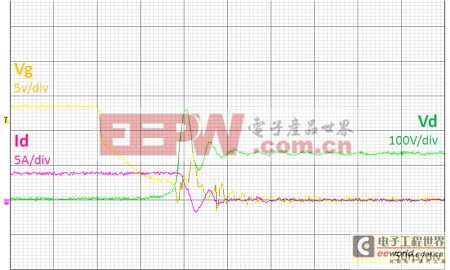

PFC是电源拓扑中对MOS要求比较高的拓扑之一,这是因为:(1)PFC有比较宽的输入电压范围。现代电源大都要求在90-264V的全范围交流电压下工作,这意味着MOS既要有足够的耐压等级又要能承受较大电流;(2)PFC的控制环路速度比较慢,为了平滑100Hz/120Hz的交流整流纹波,PFC反应时间必须达到数十ms。如果控制电路和IC没有专门进行优化,启动过程往往会产生很大的冲击电流,冲击电流可达正常工作时的5-10倍;(3)在缺乏欠压保护的PFC中,当交流电压降到低于90V很多时,电路仍有可能继续工作,这也会产生很高的开关峰值电流,导致干扰和应力超出正常范围。图6为典型的PFC电路,图7为PFC启动时,MOSFET漏极的冲击电流示意图。

图6:典型的PFC电路

图7:PFC启动,MOSFET漏极的冲击电流

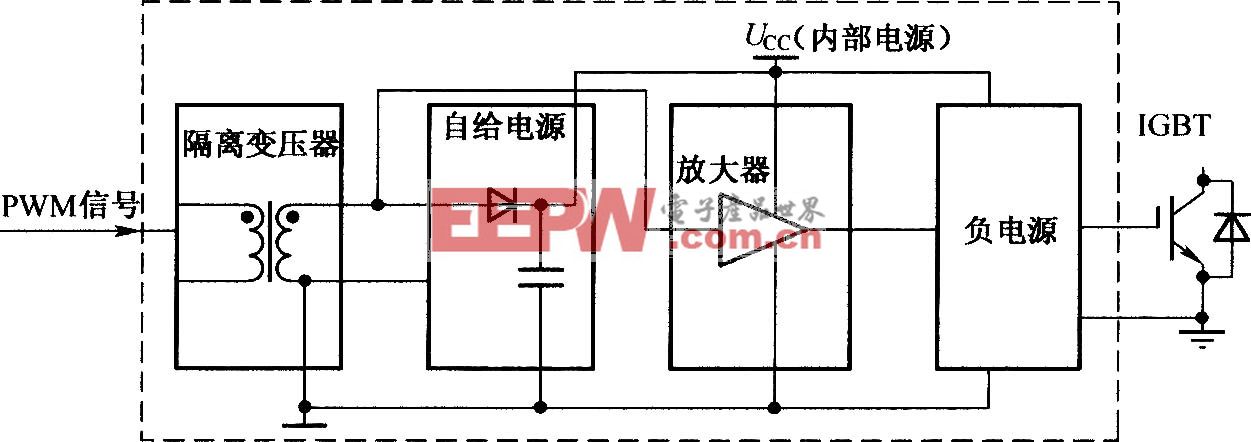

MOSFET的驱动电路已经有很多成熟的方案。在实际应用中,出于成本考虑,很多驱动电路都采用比较简单的芯片直驱方案。但是在大功率和性能要求比较高的应用中,驱动电路的设计对MOSFET的可靠性和系统的性能仍有很大影响。

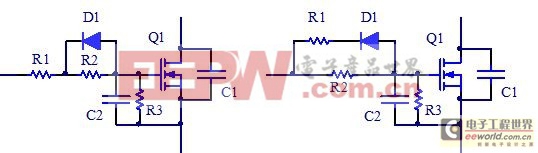

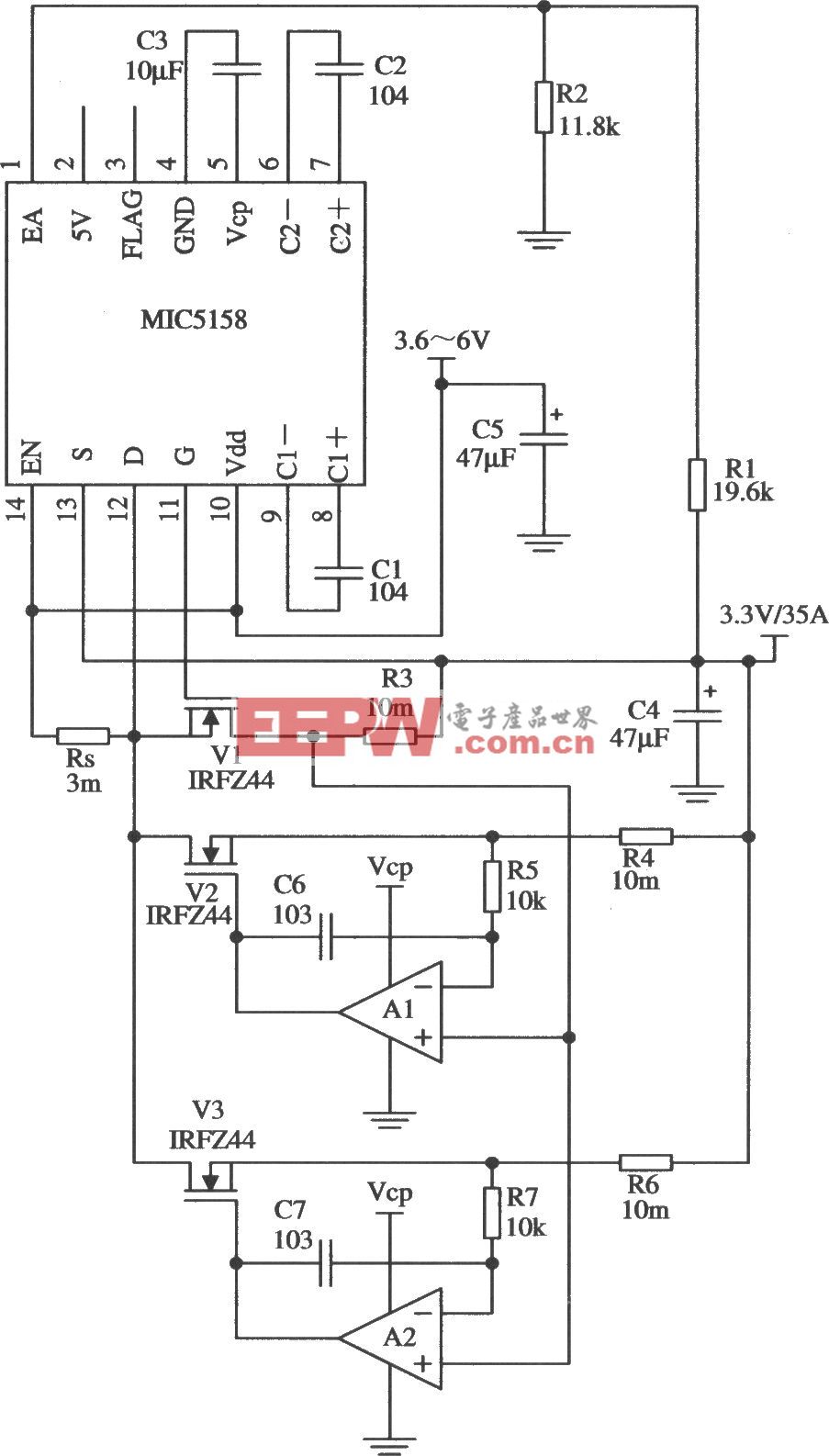

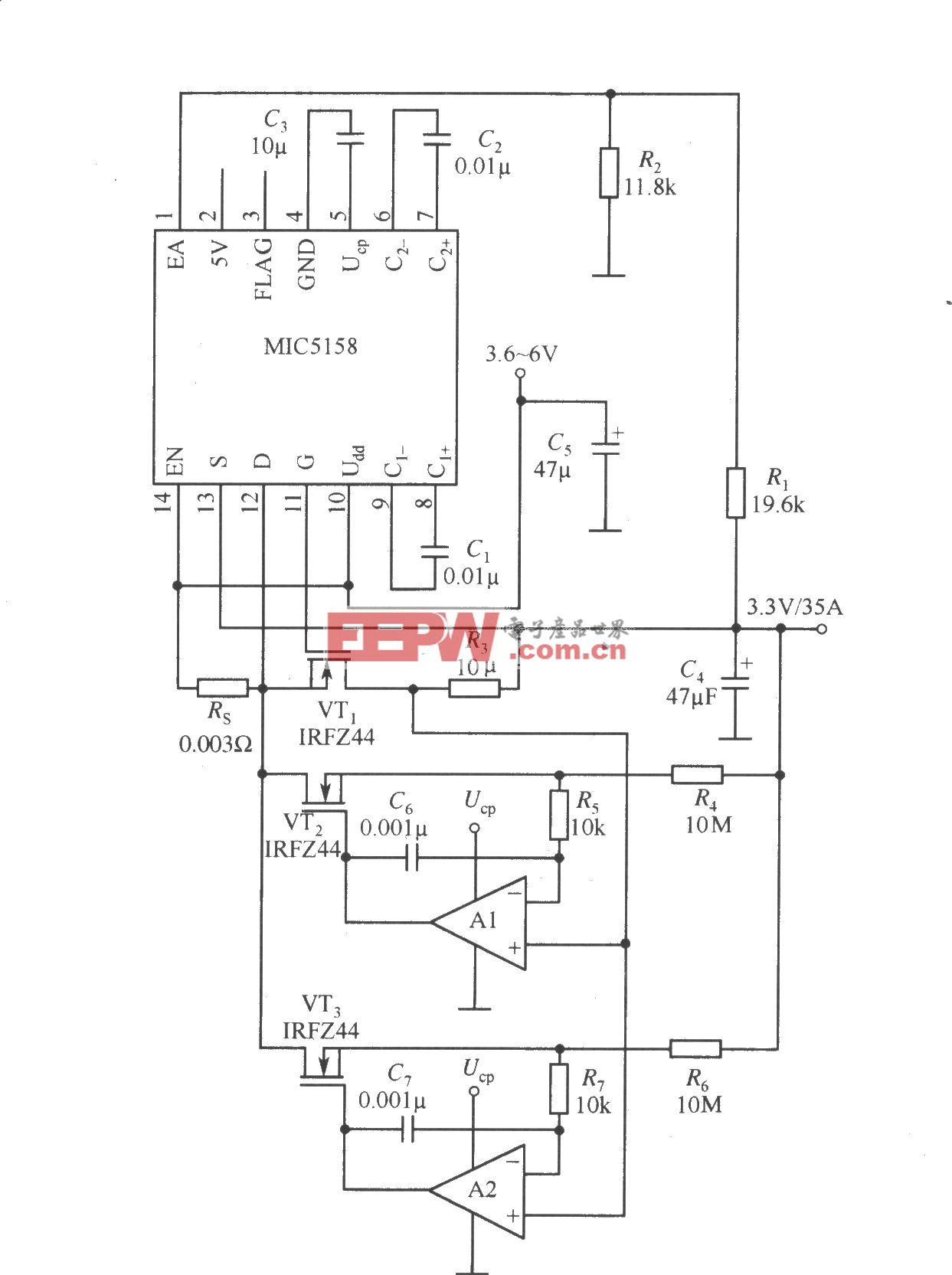

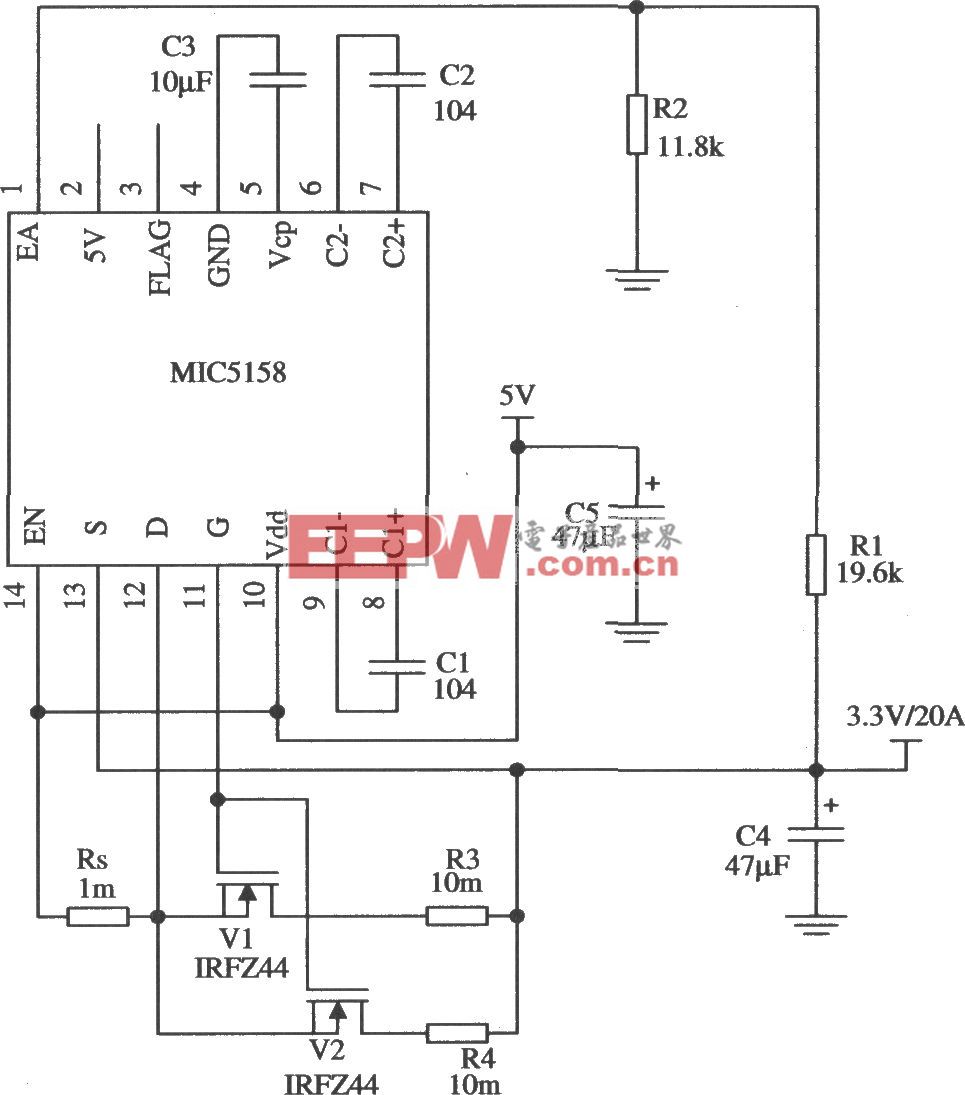

图8:MOSFET两种基本驱动电路结构

在图8中是最常见的MOSFET驱动电路,R1,R2是Rg,左图R1+R2是驱动电压上升时的充电电阻,R1单独作为放电电阻,右图R2单独作为充电电阻,R1和R2并联作为放电电阻。R3是驱动自放电电阻。C1和C2分别是外加的Cds和Cgs电容。

(1)dv/dt的控制策略和注意事项

影响dv/dt的因素有MOS自身特性、开关时的电流峰值,以及驱动电路的Rg等。由于Alpha MOS的Ciss特别小,适当的增大Cgs也是有效改善dv/dt的方法。

虽然MOSFET本身可承受的dv/dt和di/dt很高,但是根据经验数据表明,通过改变Rg和Cgs,控制dv/dt不超过20V/ns,对应的di/dt不超过200A/ns,在实际电路中能有较好的工作状态。在效率允许的情况下,dv/dt小于10V/ns,di/dt小于100A/ns更有利于可靠性,如图9和图10所示。

PFC应用中存在宽输入电压范围,输入电压跳变,以及响应时间慢等特点,容易出现比较大的冲击电流。在这种应用中需要特别注意控制峰值电流,同样的驱动参数下,峰值电流越大,开关的dv/dt和di/dt越大。要根据实际应用中的最大峰值电流来调整驱动参数。在设计中,要监测最大冲击电流下的开关波形,以确定是否需要调整驱动参数,使MOSFET工作在较好的状态。

通过漏源极增加额外的电容也可以比较容易地减小dv/dt。在正激有源拑位,桥式软开关,谐振类电路中,合适的漏源极电容有助于开关状态的优化。而在PFC和反激类电路中则需要小心处理,要和效率进行适当的平衡。在效率允许的范围内,通过增大漏源极电容还可以有效地减少EMI。

图9:MOSFET关断dv/dt与放电电阻关系

图10:MOSFET关断dv/dt与Cgs关系

(2)减少通过Cgd耦合对驱动的干扰

由于Alpha MOS的高速开关特性,以及极低的Ciss和Crss,Alpha MOS更容易受layout不良而导致驱动受到干扰。这种干扰往往是由于高频高压的走线和驱动走线靠的太近。使得漏极的高dv/dt信号通过耦合放大的Cgd进入驱动信号。如图11和图12所示。

图11:PFC MOSFET驱动被干扰

图12:PFC MOSFET驱动正常

(3)驱动端加磁珠

驱动端加磁珠是种简单合理的方法,可以抑制驱动端受干扰产生的尖刺。建议将磁珠放置在尽可能靠近MOS驱动端的位置。TO220等插件封装可以采用套管式磁珠,贴片封装的MOS可以采用类似贴片电阻大小的SMD磁珠。选取磁珠需要查阅其数据手册,确保可以通过至少3A的电流,其峰值抑制频率应在30-100MHz。通常情况下磁珠并不会对驱动波形产生影响,当MOS上流过很大电流导致干扰突然增大时,磁珠才起作用。

(4)合理放置驱动元器件的位置

对于有图腾柱驱动或者三极管辅助放电的驱动电路,起到辅助和增强作用的电路元件要尽可能靠近MOS。特别是地线,要直接单点与MOS的源级连接,一定要尽量避免在驱动的地线回路上有主功率部分的电流通过,否则,主功率回路中的大电流会耦合到驱动回路中,造成驱动的误开通和误关

评论