电源管理:满足复杂DC-DC功率转换要求

引言

在测试测量设备或嵌入式计算等工业应用中,嵌入式DC-DC转换器的系统架构可能相当复杂,在输出电压和电流、纹波、EMI及上电顺序等许多不同方面都有相关要求。本文主要探讨了DC-DC应用中转换器功率级选择的影响。

先进嵌入式DC-DC转换器的要求

许多工业系统,如测试测量设备,都需要嵌入式DC-DC转换器,是因为这些应用所需的计算能力日益增加。这种计算能力由DSP、FPGA、数字ASIC和微控制器提供,而得益于工艺几何尺寸的日益缩小,该类器件在不断的进步。另一方面,这也带来了三大要求:第一,电源电压越来越低(当然,还有容许的电压纹波和负载变化);其次,电源电流逐渐变大;第三,这些IC通常需要为内核和I/O结构以准确的顺序提供单独的电压,以避免闩锁现象的发生。

嵌入式DC-DC转换器必须具有出色的效率。这类转换器的可用空间很小,对于热设计尤其具有挑战性,因为嵌入式转换器主要依赖PCB上元件周围的铜面积来改善系统热阻抗。由于功耗与电流的平方成正比,随着负载电流的增加,这种情形会更加恶化。因此这时需要低导通阻抗RDSON、低开关损耗的电源开关。不过鉴于器件的导通阻抗RDSON越低,寄生电容乃至开关损耗就越高,最终功耗也越高,故必需进行一定的权衡取舍。嵌入式DC-DC转换器的另一个主要要求是EMI必需低。这些转换器产生的噪声会对周围的电路造成干扰,因而必须尽可能地小。不过,高速(以降低开关损耗)转换大电流(若负载所需)不可避免地会产生很大的开关噪声,包括传导噪声和辐射噪声(主要是磁场)。因此,必需特别关注功率级元件选择和布局的优化,尤其是在驱动器连接方面。此外,PWM控制拓扑也有一定影响。

举例来说,采用0.09μm技术的数字IC可能需要1.2V±40mV的电源电压。根据该DSP的数据表,其电源电流可高达952mA.另一个例子是65nm工艺制造的大尺寸FPGA,1.0V +/-50mV电源电压、85℃时,需要4.2 A的闲置电源电流。在工作模式下,按照具体配置情况,电流可增至18A,因在高开关频率下,动态要求非常高。

这些应用中包含多个不同IC相当常见,譬如,由一个较小的微控制器(电源电压较高时)来负责所有的接口和主机功能,利用一个较大的DSP或专用硬件来执行计算密集型功能。很多时候,还专门使用另有一套电压要求的高性能A/D转换器来改善噪声性能,真正充分利用这些转换器的分辨率和带宽。这些趋势催生出具有众多相倚关系的复杂的功率管理系统。

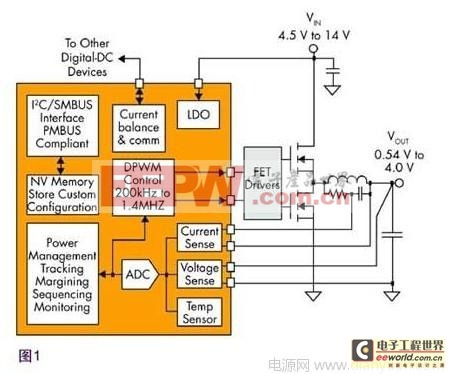

模块化控制提升系统设计

一个应用建议是把DC-DC转换器尽可能靠近负载放置。这样做可以把EMI降至最低、减小宽的大电流线迹所占用的板空间,并改进转换器的动态特性。“分布式”功率管理系统应运而生,在这种系统中,所有转换器都理想地彼此相连。能够与其它转换器在网络中协同工作的一个控制器例子是FD2004,如图1的模块示意图所示。

FD2004是Digital-DC产品系列的一员,整合了数字环路控制和高集成度功率管理功能。这种控制器及其同系列产品,可通过SMBus (系统管理总线)与主控制器和其它DC-DC转换器相连接,轻松实现许多不同的功能,如转换器的系统内配置、上电顺序、余量功能(margining)、故障保护以及系统监控。所有这些功能都有助于缩短上市时间,更重要的是,提高系统可靠性。

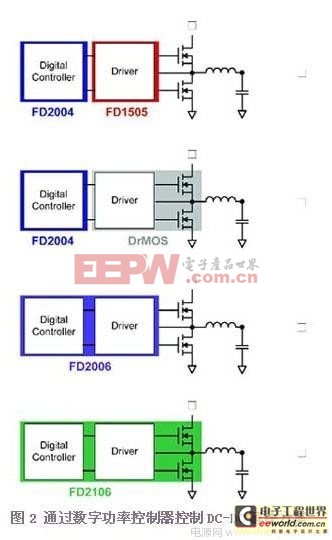

FD2004可以与外部栅极驱动器(如FD1505)和分立式MOSFET,或是集成了驱动器与MOSFET的单封装DrMOS产品协同工作。它还可以在独立式应用中通过电阻来编程—特别地,输出电压的最大值由电阻设定,且利用软件命令设定的电压最大值不得超过10%以上,以保护负载。在需要较大电流的应用中,如多相转换器,所选的架构可实现多达8个相位的电流共享,而且可在输出功率较低时实现切相(phase shedding)来保持高效率。该款控制器基于带自适应性能算法和环路补偿的数字控制环路,支持高达1.4MHz的开关频率。时钟同步可协助提升EMI性能。对于同时需要集成式驱动器和分立式外部MOSFET的应用,FD2006也是个不错的选择。

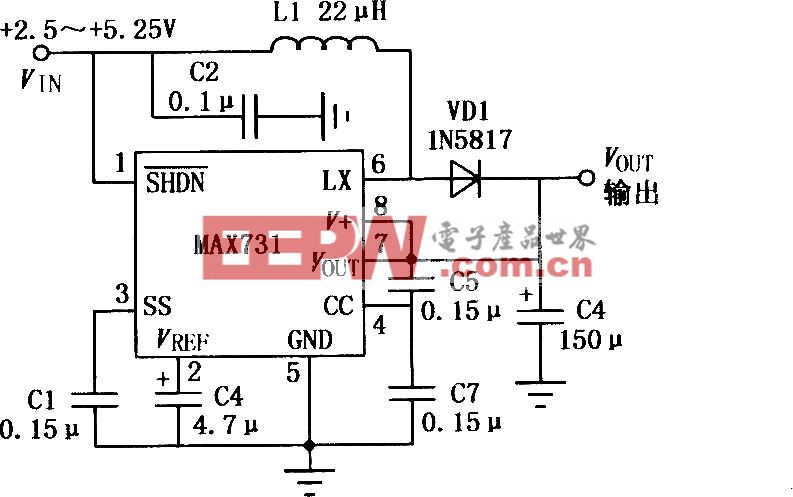

对输出电流较低的系统电压,集成式DC-DC转换器值得推荐,此时,PCB面积和易于使用都是最重要的考虑因素。数字转换器,如FD2106 (6A max),象Digital-DC系列的其它产品一样具有通信功能,可与分立式MOSFET或基于DrMOS等能提供更大电流的转换器一起使用。对独立式应用而言,由于不需要与系统内其它转换器连接,还可以采用集成式转换器(如飞兆半导体的FAN2106)。

数字功率管理系统的控制器和转换器链可通过图形用户接口来控制,很容易对所有参数和系统性能监控进行修正。这种软件运行在PC机上,并经由USB接口与控制器连接。当参数全都良好时,它们被储存在控制器的非易失性存储器中,这样PC机就不再需要运行系统了。

如图2所示的DC-DC功率级可采用不同方式设计,以同时获得最佳电气性能和热性能。

1.带驱动器和MOSFET的分立式解决方案现在仍在普遍使用。为满足所有设计要求,现在飞兆半导体提供的采用小尺寸热性能增强型MLP(QFN)封装的产品,可获得高系统性能。MOSFET实现了首先采用MLP封装(见图3所示)。其Power56和Power33产品系列采用最新的PowerTrench技术,能够同时提供超低RDSon和低Qg,从而适用于高开关频率应用。键合技术可减小封装的电感,提高封装有限的ID,适用于大电流应用。其低端FET产品组合采用SyncFET集成了肖特基二极管,在实现高开关性能的同时降低了热耗。

FDMS9600S在一个不对称的Power56封装内集成了一个高端FET和一个低端SyncFET,可进一步提高热性能,并实现小尺寸的紧凑型PCB设计(图4)。

2.上述带驱动器和MOSFET的分立式解决方案也备有8x8mm或6x6mm MLP封装的MCM(多芯片模块)。这些DrMOS(DriverMOS)产品系列包括8x8mm产品FDMD87xx和6x6mm产品FDMF67xx,可满足不同的设计要求。而评估板则可协助设计人员熟悉应用,并测试性能以便与分立式解决方案相比较(图5)。

带有Power56 MOSFET和SO-8驱动器的分立式解决方案的板卡占位面积在120mm2左右,而MCM只需要64mm2或36mm2.后者模块中的各个器件经精心挑选并全面优化,相比分立式解决方案其性能更高,热性能也更好(图6和图

评论