时域反射仪的硬件设计与实现----关键电路设计(二)

电路模拟通道有许多控制电路,基本上都可以通过FPGA来完成,比如衰减倍数控制、交直流祸合,接地控制、使能控制、通道较准控制等,这些都可以通过常规的高低电平来完成。考虑到前端电路需要的控制信号线较多,如果直接由FPGA来控制,必定会占用较多的I/O口,同时从布线的角度来考虑的话,大量的连线从后端连接到前端,必定会使用较多的板上面积,给整体布线带来许多麻烦。为此本设计摒弃了直接控制方式,而采用间接控制,所有的控制任务只需要三条控制线和一个或多个串并转换器CD4094就可以完成。

该串并转换器有四个输入端,八个并行输出端和一对互补的串行输出端。四的输入端中包括:串行数据输入、时钟信号输入、选通控制、使能输出控制。串并转换器内部主要由三大部分组成:移位寄存器、数据锁存(选通)器和三态缓冲器。时钟信号将串行数据以先后的顺序存到移位寄存器,每一个时钟对应一位数据,选通控制端则控制是否将旧数据用新数据代替,如果选通控制器一直处于低电平,则并行输出端的数据还是上一次的数据,如果选通控制在新数据到来之前已经是高电平,则如果使能输出为高,从并行输出端的数据随着时钟到来依次得到更新。如果是经过八个串行时钟以后,选通控制信号由低到高的变化,则并行数据端的八位输出数据同时得到更新。串并转换器的两个串行输出端口可以用来对数据位数的扩展,即实现多个串并转换器的级联。

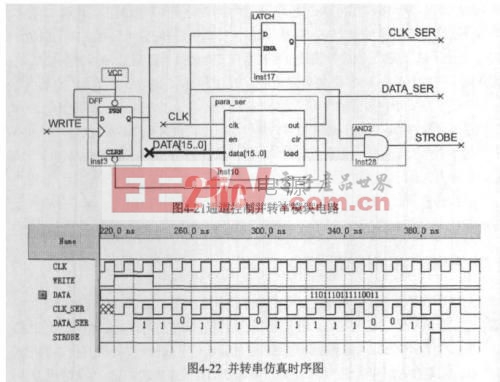

在FPGA内部同样存在一个并转串的模块,它将从ARM送过来的通道所需要的并行控制型信号转换成对应的串行信号,转换模块通过verilog HDL(硬件描述语言)来实现。该模块结构和仿真时序图,如图4-21和4-22所示。

从时序图可以看到当W叹仃E信号产生一个上升沿以后,16位的并行数据随着时钟的增加,依次从最高位开始串行输出,当最低位输出以后STROBE在最后一位数据产生半个时钟周期以后产生一个上升沿,该上升沿可以用来控制在通道中的串并转换器的选通控制引脚,使级联的两个串并转换器的并行输出端同时得

到更新。CLK_SER输出用来为串并转换器提供所必须的时钟信号。

在最初的设计当中,考虑到数字电路的设计简单和方便,对通道的控制信号的写入采用的是循环写的方式,即写完一次以后紧接着写第二次,无论数据是否更新,CD4094一直都有数据写入。后来发现通过这种方式对通道进行控制,导致了一些不必要的麻烦。首先是控制信号很多都与被测信号有一定的联系,如果不停的循环写,则把噪声信号引入到了被测信号上。另外对通道上的控制信号的修改次数相对于循环写的次数来说,修改的次数远远小于写的次数,也就是说很多次的写操作都是没有任何意义。为此将对通道上的控制信号的写入采用由ARM来控制,即在ARM读取一次FPGA内部RAM中的数据并显示完以后,就进行一次对通道控制的写操作,只需要在图4-21中的WRITE端产生一个上升沿即可。这样即消除了噪声的引入,同时也保证了数据的更新。

评论