时域反射仪的硬件设计与实现----关键电路设计(三)

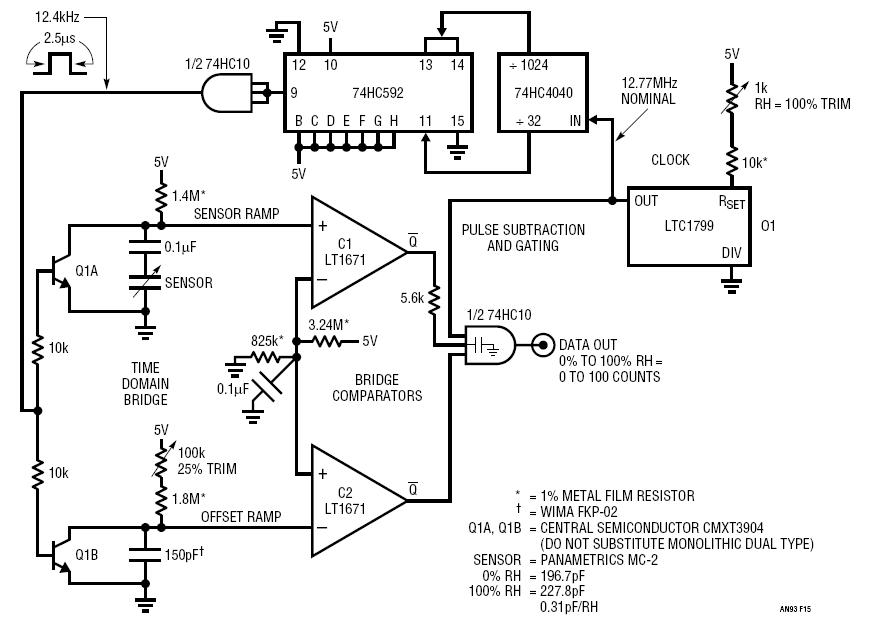

在ARM读取RAM内部的数据时,此时RAM计数器的计数时钟已经换成由ARM来提供,即ARM通过I/O口产生一个上升沿信号,送给地址计数器。在读取数据的时候,RAM地址计数器并不是从零开始从新计数,而是继续从D点所在的地址继续计数,则D+1号地址所对应的数据应该是被认为在整个储存深度(3K)中的第一个数据,从D+l到C点则为1K的预触发数据,从C到D则为后触发数据。因此根据触发信号到来的偶然性,每一次从RAM中读取数据时,C点和D点所对应的RAM的地址不一定都相同,但是ARM从RAM中读回的数据,经过从新排列,保证每次采集到的数据的前1K点就是预触发数据。这样经过软件处理显示到屏幕上以后,波形不仅可以前后移动,同时也保证了触发的稳定。

评论