时域反射仪的硬件设计与实现----关键电路设计(三)

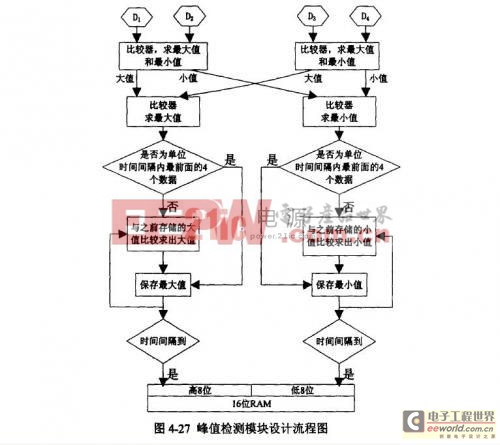

在时域反射测量中,在高速时基情况下,如100ns/div--5ns/div之间,屏幕上的一列对应了ADC单次采样采集到的数据,即点对点形式,此时ADC也处于最高速采样状态下(250MSPS),当时基为20ns/div时,采样率仍保持在250MSPS,此时屏幕上的单个像素点对应的时间间隔为5ns,对应了两次采样时钟,即两个数据确定了屏幕上的一列图形,如果这两个数据相同,则对应屏幕上的一点,如果不同,则对应屏幕上同一列的上下两个或是连成一小段的像素点。当时基为500ns/div,如果采样率仍为250MSPS,则单个像素点的时间(20ns)对应5次采样的数据,如果采样率为200MSPS,则单个像素点的时间(20ns)对应4次采样的数据。又因为为了降低功耗的目的,在1us/div以后都采用了100MSPS,单个像素点的时间(20ns)对应了以4为倍数的采样数据。为此在500ns/div时也采用200MsPs,这样在进行峰值检测的时候可以一次将4个数据送到高速比较模块做流水线比较,并在规定时间周期内找到最大值和最小值。4个高速数据的峰值比较电路设计流程如图4-27所示。

在FPGA内部,峰值检测模块电路由于采用了流水线的模式,因此用了较多的8位并行D触发器、8位比较器和8位两路选择器来实现。虽然占用了一定的FPGA的内部逻辑单元(LB),但却保证了大量数据的高速连续处理,且不丢失有用的数据,唯一的缺点就是实时性不强,即4个数据的比较需要经过好几次时钟(每个时钟为周期为4*4ns)以后才能找到最大值和最小值,即有一定的延时性,但并不影响波形的正常显示。因此这种流水线的操作方式实际上是一种利用空间换取时间的方式。整体设计模块如图4-28所示。

在峰值检测模块当中,输入端有两个控制输入,CLK_NUM和OVER_4.OVER_4表示峰值检测在单位时间内总共多少个数据进行比较,因为在时基为500ns/div和1us/div下,一次只进行4个数据的比较,就要输出最大和最小值,而在Zu叮div以后都是要进行大于4个,且以4为倍数的数据的比较,而模块单次只能比较4个数据,因此用OVER4来控制总共比较的数据是否大于4,大于4则OVER_4为1,反之为O。CLK_NUM用来控制单位时间间隔内到底有多少个数据进行比较,如果CLK-少旧M的周期为16ns,则只有4个数据比较,此时OVER_4也为0,当CLK_NUM的周期为16ns的倍数后,则会有4的倍数个数据进行比较。

实际上CLK-少旧M的周期与时基是相联系的,如时基为500ns/div,则CLK_NUM的周期为20ns,又因为此时的采样率为20OMSPS,所以只有4个数据比较,当时基为1us/div,CLK_NUM的周期为40ns,采样率为100MSPS,所以同样只有4个数据比较,而当时基为2us/div,CLK_NUM的周期为80ns,采样率为100MSPs,就会有8个数据进行比较,而在比较的过程当中,先进去的4个数据会比较出一个大值和小值,这两个数据被默认为最大值和最小值暂时保留下来,直到与后进来的4的数据比较出的大值和小值继续做比较,最终确定最大值和最小值。表4-3给出了在不同时基情况下起用峰值检测模块控制信息相关对照表

评论