时域反射仪的硬件设计与实现----关键电路设计(三)

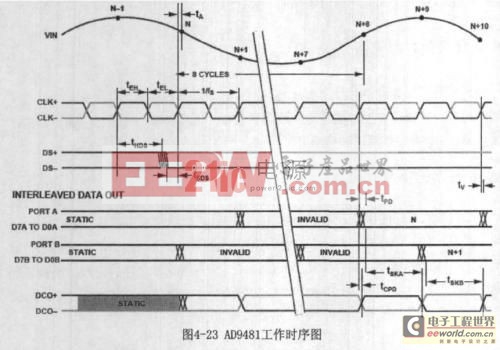

AD9481数字部分的输出采用的是交替输出,即输出分为八位并行的A口和B口。模数转换器在每一次时钟的上升沿进行采样,当第N个采样时钟到来时,A口输出一个新的八位并行数据,B口保持上一次输出数据不变;当N+l次采样时钟到来时,B口输出一个新的八位并行数据,A口八位数据保持不变。则通过上述方式,实际上A、B口的输出频率最高也只有125MHz(25OMsPS),信号输出频率降低了一半,减缓了高速数据存取对读写控制的要求,减小了数据在存储过程当中产生错误的可能性。

ADC采样的时钟信号由FPGA提供,ADC的采样时钟分为三种情况:250MHz、200MHz、100MHz.系统所用的时钟则由50MHz的有源石英晶体提供,50MHz的时钟送给FPGA以后,通过FPGA内部的一个PLL(锁相环),即可产生以上三种高速时钟信号。

3.3.2峰值检测

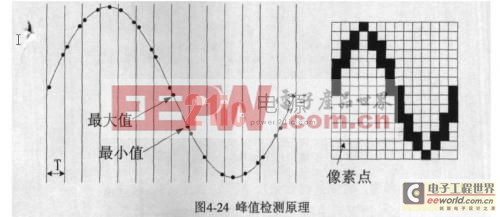

峰值检测是数据采集系统中比较常用的方式,对于捕获毛刺信号具有很大的帮助。它不像正常取样方式那样,通过采集大量与信号有关的数据,存储在大型存储器中(兆量级),而是仅仅存储了少量能够反应信号真实形状的有效数据,占用了极少的存储空间,在不增加存储深度的情况下,准确的捕获到毛刺和偶发事件,同时峰值检测采样形式还能防止显示出现差拍效应和具有包络显示功能[切。

峰值采样的基本原理就是以尽可能高的采样率对信号进行采集,在单位时间内对采集到的数据进行高速比较,从中找出最大值和最小值并保持下来,而将其它值忽略掉,在显示方面依靠采集到的最大值和最小值可以比较真实的还原出原始信号的一些特性。如图4-24所示,在周期时间T内(对应屏幕上一个像素点的时间),信号被高速采样,采样点数大于等于2,所有被采集到的数据都被直接送到FPGA内部进行高数比较,找到最大值和最小值(如左图中黑点部分)。在周期时间T结束之前,将比较出的最大值和最小值保存在FPGA内部的RAM中,当ARM读到这两个数值时,通过软件处理,很容易就在屏幕上恢复出与原信号相似的波形。右图中黑色像素点对应ARM读到的最大值或最小值,灰点由硬件产生。

图4-25显示了利用峰值检侧来捕获毛刺信号的优点。在没有峰值检测情况下,当信号上出现较窄的毛刺信号的时候,由于采样点间隔大于毛刺信号的宽度,因此恢复出的信号上并不能显示出毛刺信号;而在使用峰值检测采样以后,由于采样间隔小于毛刺信号的宽度,则必然会捕获到毛刺信号,其捕获毛刺信号的能力取决于采样间隔,一般宽度大于采样间隔的毛刺信号都可以捕获到。这种捕获毛刺和偶发事件的能力在检测维修当中十分有用。

差拍现象(混盛)是由于采样没有遵循Nyquist采样定律导致的结果,当示波器工作在慢速时基档位(此时采样速率较低),而

评论