降低从中间总线电压直接为低电压处理器和 FPGA 供电的风险

工业、航天和国防系统通常采用额定 24V~28V 的中间总线电压,在这些系统中,串联电池作为备用电源,但是,由于分配损耗,并不适合采用 12V 总线体系结构。系统总线和数字处理器电源输入之间较大的电压差在电源分配、安全和解决方案规模上带来了设计难题。如果使用单级非隔离降压DC/DC 转换器,那么,必须工作在非常精确的 PFM/PWM 定时上。输入浪涌事件对 DC/DC 转换器提出了更严格的要求,对负载存在另一个过压风险。由于制造中导致的错误或假冒电容,这会使得输出电压偏离超出负载额定范围,有可能导致 FPGA、ASIC 或者微处理器被烧坏。取决于受损程度,很难确定故障根本原因所在,最终高昂的维修成本、停机时间以及对声誉的损害都会令人非常沮丧。

本文引用地址:http://www.eepw.com.cn/article/228072.htm因此,应该非常仔细的考虑怎样减小过压风险,从而降低成本,减少给客户带来的不便。采用了熔丝的传统过压保护方法并不适用于保护现代 FPGA、ASIC 和微处理器,特别是上游额定电压是 24V 或者 28V 的情况。开发了新解决方案,结合额定 38V 的 10A DC/DC 开关稳压器和电路以解决很多故障问题,包括输出过压等。当今最先进的数字逻辑器件的供电和保护功能可以在一个紧凑封装器件中实现。

随着输入电压和浪涌的增大,精确的开关定时越来越重要

当输入电压和所需要的输出电压之间存在较大的电压差时,一般会采用效率很高的开关DC/DC 稳压器。为实现简便的解决方案,最好选择非隔离降压开关转换器,其工作频率足够高,以减小电源磁体和滤波器电容的尺寸。但是,这种 DC/DC 开关转换器必须工作在低至3% 的较窄的占空比条件下,这就需要精确的 PWM/PFM 定时。而且,数字处理器需要严格的电压稳压,要求快速转换响应以确保电压在安全限制范围内。在较高的输入电压时,会降低 DC/DC 稳压器顶部开关接通误差余量。

总线电压浪涌一般出现在航天和国防应用中,不仅仅对 DC/DC 转换器造成损害,而且也会损害负载。必须对 DC/DC 转换器进行额定以采用高速控制环对过压浪涌稳压,从而获得足够的电压抑制。如果 DC/DC 转换器无法稳压,或者不能承受总线浪涌,那么负载上就会出现过压。负载的旁路电容由于老化或者温度原因致使性能下降也会引起过压故障,导致在产品寿命末期出现宽松的瞬态负载响应。如果电容劣化超出了控制环的设计限制,那么,两种机制导致负载出现过压。首先,即使控制环保持稳定,严重的瞬态负载突变事件也会导致电压偏离远远高于设计初衷。其次,如果控制环是条件稳定的 (或者,更差一些,不稳定),输出电压峰值会不断震荡,超出了可接受的范围。如果采用了不正确的绝缘材料,或者假冒元器件进入了制造环节,那么,电容也会意外劣化,过早失效。

便宜的假冒元器件会导致代价高昂的问题

在灰色市场或者黑市上,低成本假冒元器件不会真正满足标准要求 (例如,这些元器件是经过回收的,从电子垃圾中重新加工制造,或者采用劣质材料制造),即使这样,有的人抵挡不住假冒元器件的成本诱惑。当假冒产品失效时,暂时的低成本就会成为昂贵的开支。例如,假冒的电容会以多种方式失效。假冒钽电容内部自发热非常严重,其正反馈机制导致散热出现失控。假冒陶瓷电容含有粗糙劣质的绝缘材料,随着元器件的老化或者工作在较高温度时,电容量都会加速下降。当电容容量大幅度下降引起控制环不稳定时,电压波形振幅要比最初设计值大很多,对负载造成损害。

在业界不幸的是,假冒元器件越来越多的进入了供应链和电子制造流程,即使是最敏感和最安全的应用。美国参议院武装部队委员会 (Senate Armed Services Committee - SASC) 在 2012 年 5 月公布的报告中指出,军用飞机和武器系统中出现了越来越多的假冒电子元器件,极有可能影响系统的性能和可靠性。这些系统都是由国防工业顶级承包商制造的。这类系统中的电子元器件日益增多,例如,新的联合攻击战斗机有 3500 多个集成电路,假冒元器件带来了系统性能和可靠性风险,决不能忽视这一问题。

怎样降低风险

任何降低风险计划都应考虑系统将怎样对过压状况做出响应并从过压状态实现恢复。倘若过压故障有可能导致烟雾或火情,这可以接受吗? 查明根源及实施整改措施的工作会由于过压故障造成的损坏而受阻吗? 如果本地操作员对受损系统重新供电 (重新启动),尝试恢复系统,这会对系统造成更大的损害吗? 确定故障原因并恢复正常系统工作需要哪些过程,要花费多长时间?

传统保护电路的不足

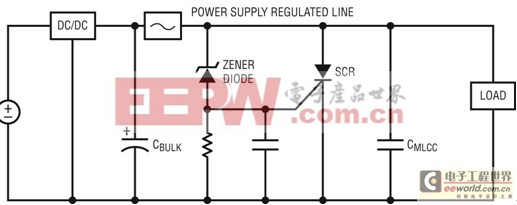

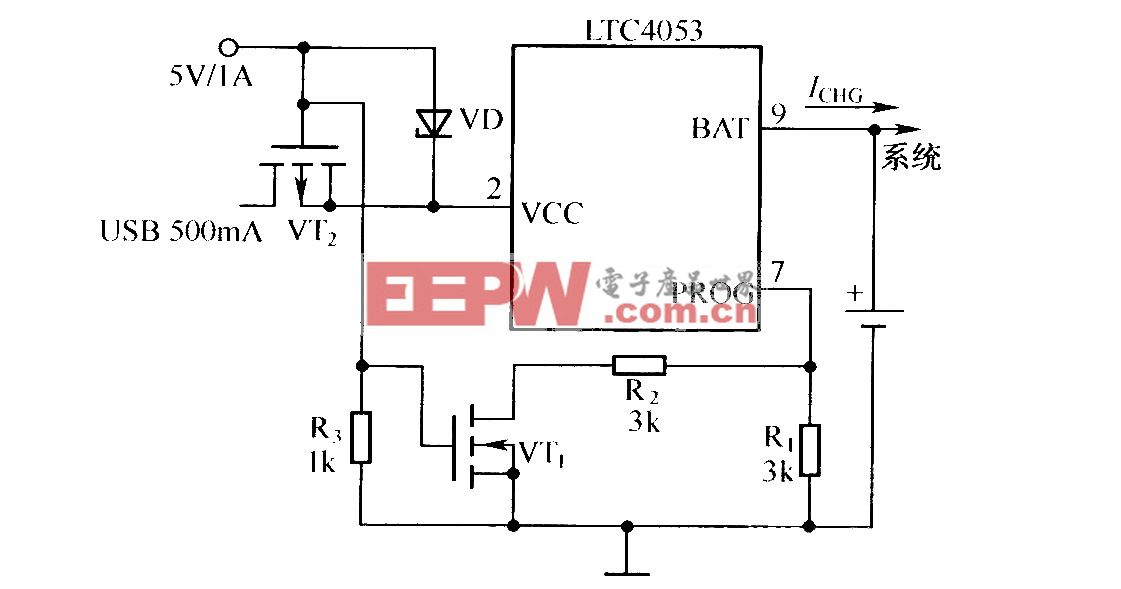

传统的过压保护方法包括熔丝、可控硅整流器 (SCR) 和齐纳二极管。这一电路 (图1) 通过以下方式来保护负载。如果输入供电电压超过了齐纳击穿电压, SCR 触发,吸收足够的电流,熔断上游熔丝。这一方法相对简单,而且成本低,但是,其缺点包括齐纳二极管击穿电压的精度、SCR 栅极触发门限变化、SCR 和熔断响应时间的变化、以及从故障中恢复所需要付出的努力等 (例如,实际处理熔丝,并重新启动系统)。如果待考虑的电压源对数字内核供电,由于大电流时的正向电压降与最新数字处理器的内核电压相当,甚至高于内核电压,那么,SCR 的保护功能非常有限。考虑到这些缺点,传统的过压保护方法并不适用于高压至低压 DC/DC 转换供电负载,例如,价格比较昂贵 (不上千都可能要几百美元) 的 ASIC 或者 FPGA。

图1: 传统的过压保护电路包括熔丝、SCR和齐纳二极管。虽然成本低,但是这一电路响应时间不足以实现对最新数字电路的可靠保护,特别是上游供电电源是中间电压总线的情况。而且,即使从过压故障中进行最简单的恢复也很麻烦并非常耗时。

结合了电源和保护电路的最新创新

更好的解决方案是准确地探测到即将出现的过压情况,迅速

评论