高性能模数变换器设计变压器耦合型前端的方案

ADC可以分为两种类型:带有缓冲的和不带缓冲的。无缓冲ADC的功耗往往要远大于缓冲ADC,但是缓冲ADC更容易驱动。

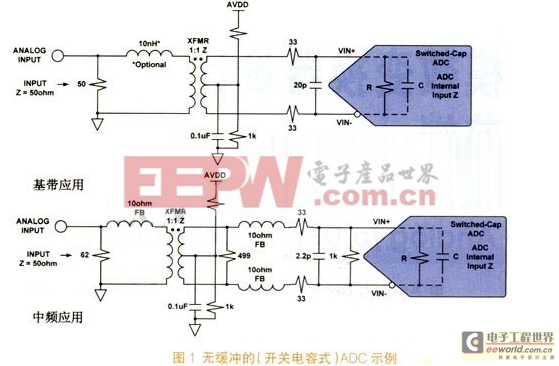

开关电容ADC是一种无缓冲的ADC的一个具体例子。前端设计则直接与ADC内部的采样-保持电路(SAH)网络相连接。这就带来了两个问题:一是ADC的输入阻抗会随着时间和模式不同而发生变化;第二种则是电荷注入,它会反映到ADC的模拟输入上,这会带来滤波器稳态建立(filter settling)方面的问题。

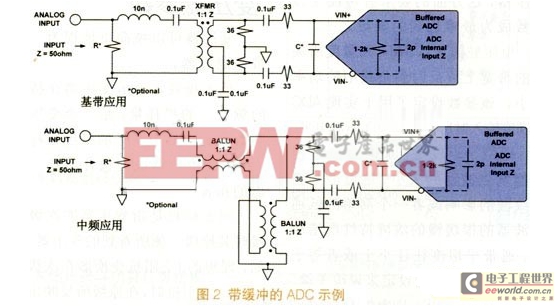

带有缓冲的ADC的理解和使用最为方便。通过采用能够抑制电荷注入带来的尖峰的隔离缓冲器,可以显著降低开关的瞬态。与开关电容ADC中的情形不同,输入的端接特性在整个规定的ADC带宽上不会随着模拟输入频率的不同而发生变化,恰当的驱动电路的选择将变得更为方便。带缓冲的输入级的不利之处,就在于会使得 ADC消耗更多的功率。设计示例

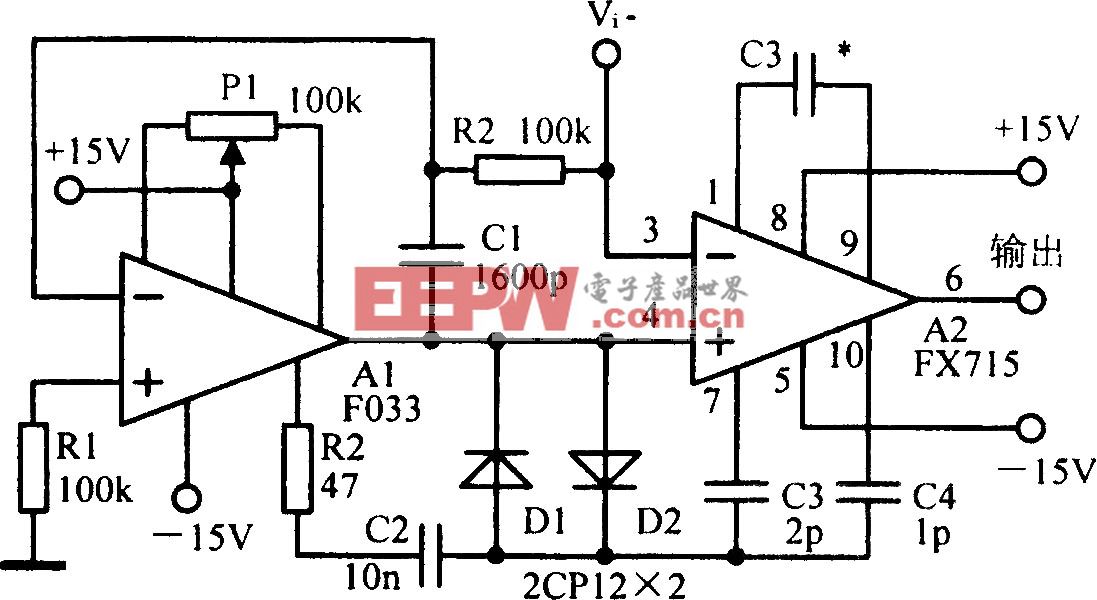

基带和IF应用的设计实例,分别如图1和2所示。

在基带应用中,ADC的输入阻抗一般都很高,因此输入的匹配的重要性较低,而且也更容易实现。往往一、两个小量值的、用于衰减电荷注入效应的串联电阻外加简单的差分输入电容就够用了。这样一来,就只需要一个简单的滤波器,来衰减宽带噪声,以获得最优的性能。

高频应用则需要设计者作多一些思考。要优化输入的匹配,就需要通过前端跟踪模式阻抗的匹配来让输入的阻抗尽可能呈阻性。使用串连或并联的电感或铁氧体磁珠(在图中示出的是前者),可消除“电容”项。

总之,对输入进行匹配可以给出良好的带宽、增益平坦度(功率驱动的变化更小)和更为出色的性能。

带缓冲的ADC的基带应用同样使用一个简单的网络,类似于开关电容ADC的配置。请注意,应对副边进行端接来将其与原边的输入相匹配。

在图2中,针对高IF应用使用了双balun(平衡/非平衡转换)。这就使得输入在高达300MHz的范围内能得到很好的保持平衡,让二阶失真始终最小化。

小结

设计中必须考虑多种参数,以实现最佳性能。变压器千差万别。设计者若能理解特定的变压器性能参数,并向制造商咨询没有给出的参数,就能够更好预测出其设计的特性。高IF设计对于变压器的相位非平衡性很敏感,因此这些设计可能需要两个变压器或者balun。

了解所采用的ADC是缓冲型还是非缓冲型也很重要。不带缓冲的 ADC的输入阻抗随时间而变化,在高IF情况下,相应的设计也更为困难。为了优化设计,输入应该实现跟踪匹配。使用磁珠或低Q的电感来消除开关电容ADC 的输入电容分量。这可以最大限度地提高输入带宽,实现更优化的输入匹配,并维持SFDR性能。缓冲的ADC的设计较为方便,即使在高IF下也是如此,但它们的功耗更大。无论使用何种ADC类型,基带应用的设计工作最简单。

评论