电子菜鸟入门电路基础概念:TTL与CMOS电平 / OC门

2.输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。

3.输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的电平值都必须大于此Voh。

4.输出低电平(Vol):保证逻辑门的输出为低电平时的输出电平的最大值,逻辑门的输出为低电平时的电平值都必须小于此Vol。

5. 阀值电平(Vt):数字电路芯片都存在一个阈值电平,就是电路刚刚勉强能翻转动作时的电平。它是一个界于Vil、Vih之间的电压值,对于CMOS电路的阈值电平,基本上是二分之一的电源电压值,但要保证稳定的输 出,则必须要求输入高电平> Vih,输入低电平

对于一般的逻辑电平,以上参数的关系如下:

Voh > Vih > Vt > Vil > Vol

6.Ioh:逻辑门输出为高电平时的负载电流(为拉电流)。

7.Iol:逻辑门输出为低电平时的负载电流(为灌电流)。

8.Iih:逻辑门输入为高电平时的电流(为灌电流)。

9.Iil:逻辑门输入为低电平时的电流(为拉电流)。

门电路输出极在集成单元内不接负载电阻而直接引出作为输出端,这种形式的门称为开路门。开路的TTL、CMOS、ECL门分别称为集电极开路(OC)、漏极开路(OD)、发射极开路(OE),使用时应审查是否接上拉电阻(OC、OD门)或下拉电阻(OE门),以及电阻阻值是否合适。对于集电极开路(OC)门,其上拉电阻阻值RL应满足下面条件:

(1).RL (VCC-Voh)/(n*Ioh+m*Iih)

(2).RL > (VCC-Vol)/(Iol+m*Iil)

其中n:线与的开路门数;m:被驱动的输入端数。10.常用的逻辑电平

·逻辑电平:有TTL、CMOS、LVTTL、ECL、PECL、GTL;RS232、RS422、LVDS等。

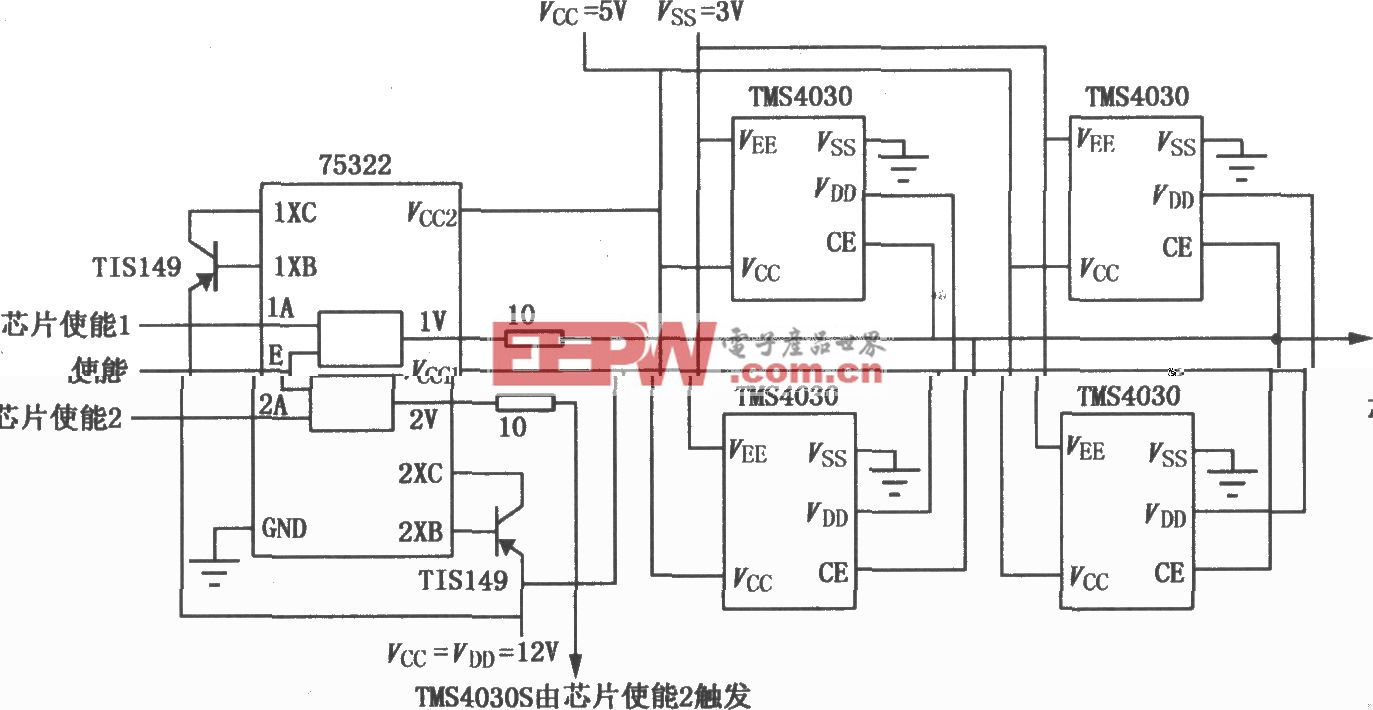

·其中TTL和CMOS的逻辑电平按典型电压可分为四类:5V系列(5V TTL和5V CMOS)、3.3V系列,2.5V系列和1.8V系列。

·5V TTL和5V CMOS逻辑电平是通用的逻辑电平。

·3.3V及以下的逻辑电平被称为低电压逻辑电平,常用的为LVTTL电平。

·低电压的逻辑电平还有2.5V和1.8V两种。

·ECL/PECL和LVDS是差分输入输出。

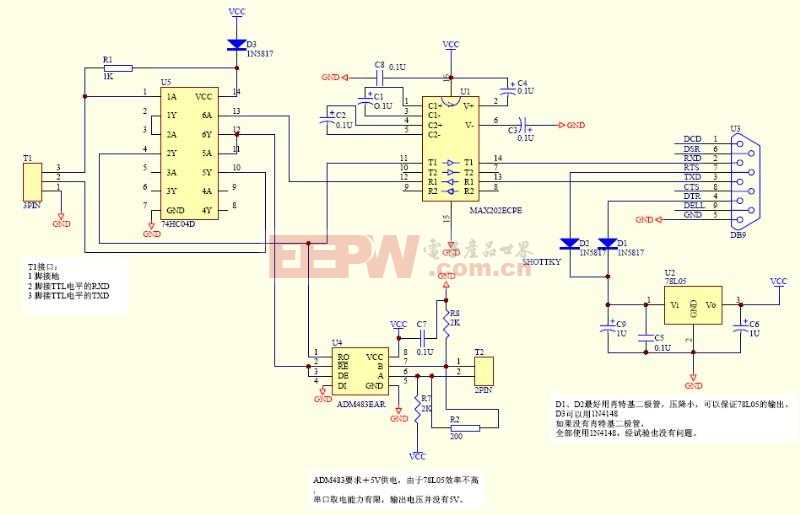

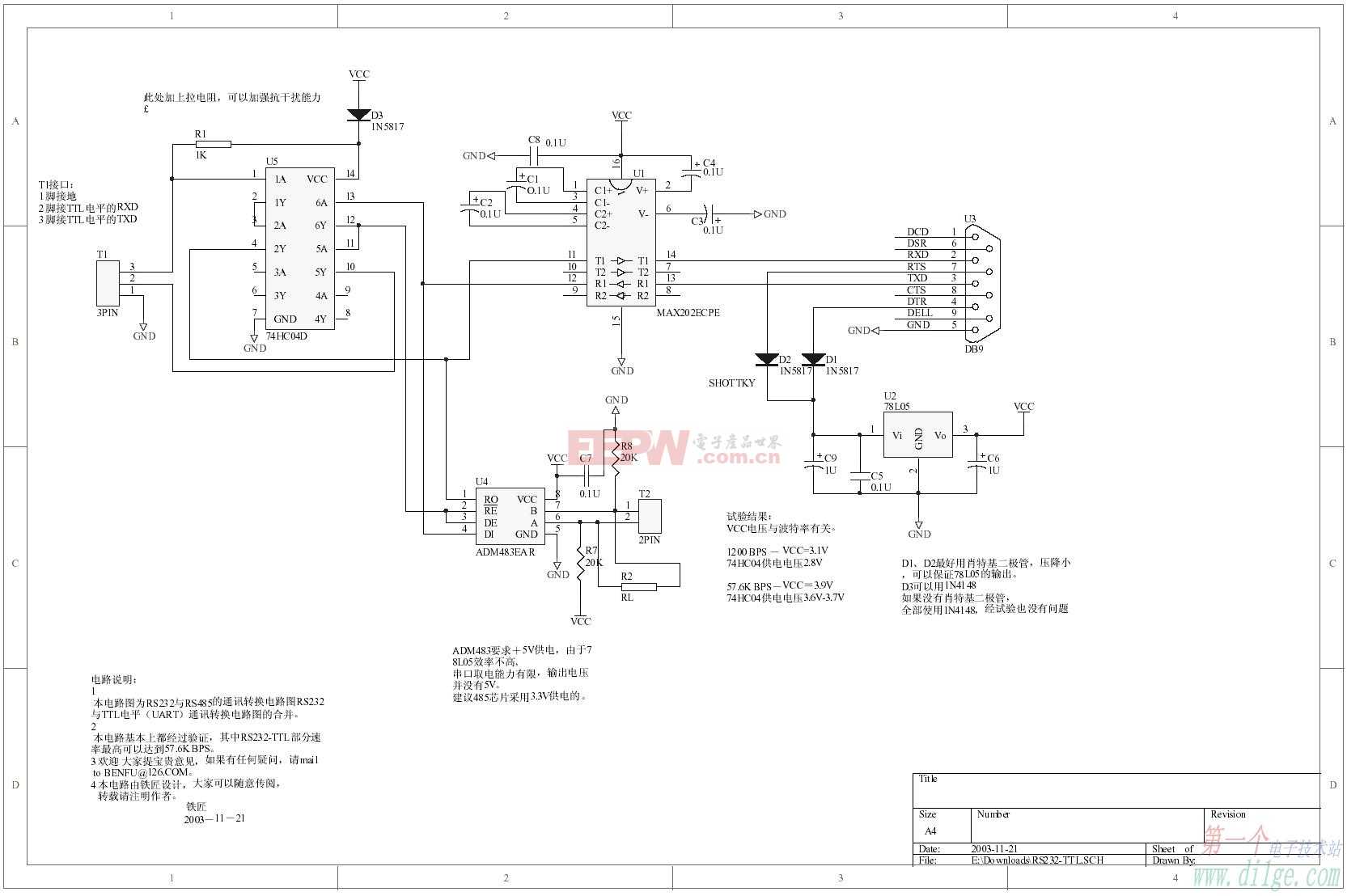

·RS-422/485和RS-232是串口的接口标准,RS-422/485是差分输入输出,RS-232是单端输入输出。

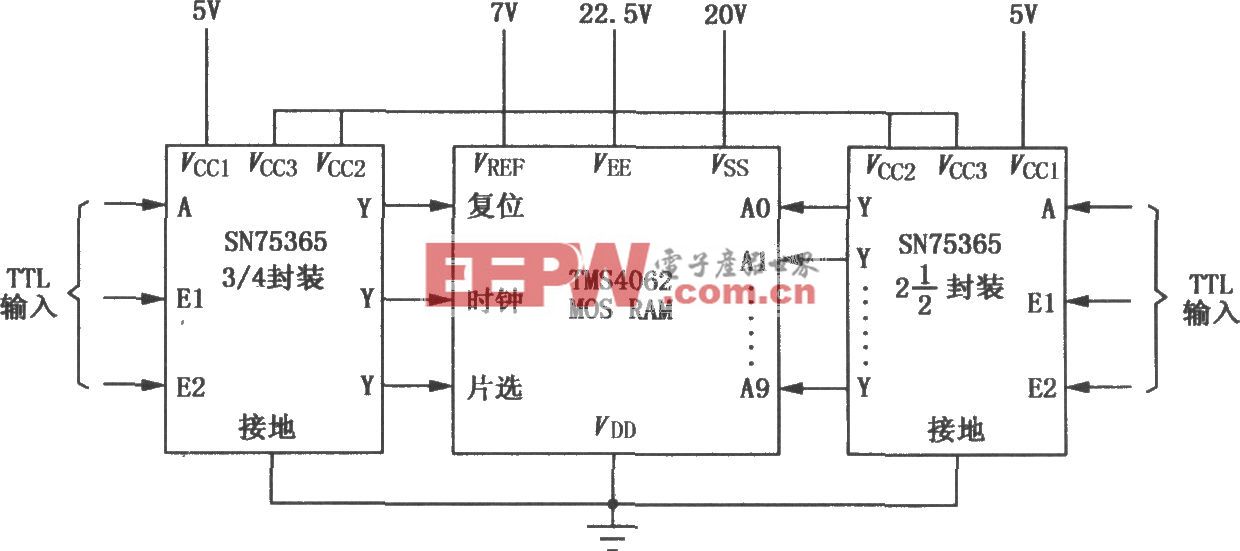

OC门,又称集电极开路(漏极开路)与非门门电路,Open Collector(Open Drain)。

为什么引入OC门?

实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态电平)用同一条导线输送出去。因此,需要一种新的与非门电路--OC门来实现“线与逻辑”。

OC门主要用于3个方面:

1、实现与或非逻辑,用做电平转换,用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

2、线与逻辑,即两个输出端(包括两个以上)直接互连就可以实现“AND”的逻辑功能。在总线传输等实际应用中需要多个门的输出端并联连接使用,而一般TTL门输出端并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件。在硬件上,可用OC门或三态门(ST门)来实现。 用OC门实现线与,应同时在输出端口应加一个上拉电阻。

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理 上拉电阻相关文章:上拉电阻原理

评论