等离子处理提高65nm逻辑器件可靠性

测试

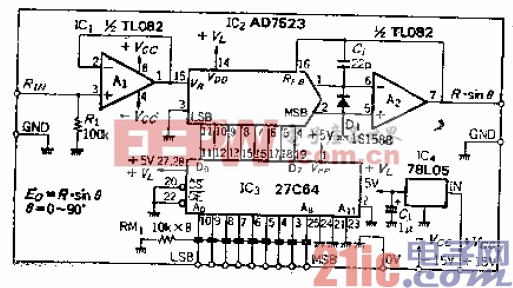

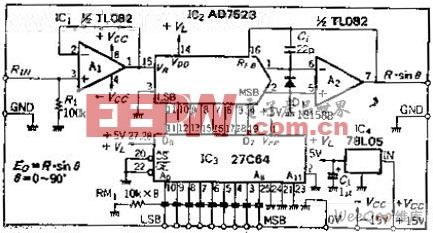

基于上述研究结果,在65nm逻辑流水线上测试了得到的SiN阻挡层工艺。在Cu CMP和SiN扩散阻挡层淀积间的等待时间是保证65nm逻辑制造生产率的关键因素。执行的基线等待时间是2小时。在结构晶圆上作了不同的6组实验(见表1)。从这些实验得到的数据显示,用SiN工艺可得到可靠的优良VBD性能。

由于改善了的阻挡层和预处理工艺,Cu CMP和SiN扩散阻挡层淀积间的等待时间可从2小时增至8小时,提供了较大的制造灵活性。

结论

通过优化的SiN阻挡层工艺和Cu表面等离子预处理,成功地制备了高VBD SiN扩散阻挡层薄膜。VBD性能和可靠性的极大提高可归因于SiN体薄膜内Si-H键减少,以及SiN体薄膜淀积前用NH3预处理后Cu/SiN界面上C和O污染大大减少。

评论