可编程芯片:拼合成一个模拟解决方案

不同的隐喻(metaphor)

芯片开发者倾向于向用户隐藏起可编程芯片的结构,而代之以一种隐喻来虚拟化结构。他们希望,这种虚拟化对用户更熟悉,对要解决的问题更有相关性。隐喻会随硅片的结构,以及供应商对于客户与客户问题的观点而变化。例如,在数字PLD的早期,供应商将一只PLD的内部描述为多组NAND门驱动大型NOR门输入端,以后成为了表述逻辑功能的标准方法。

当FPGA出现时,其供应商初期将其描述为大型的逻辑单元阵列,每个单元都包括一些门和一个触发器。这些隐喻都非常接近于芯片的实际电路。现在,FPGA已变得如此庞大,隐喻已更抽象。今天,看待FPGA的典型方法是将其当作一个空白单子,一个人在上面书写RTL(寄存器传输级)逻辑,有便于布放分配的内存块、DSP(数字信号处理)块,以及高速I/O单元。没人再尝试使隐喻反映出电路情况。

从供应商为自己可编程模拟器件所选择的隐喻中可以看到一种类似的差别。以Lattice为例,它对自己电源控制器IC的描述用词接近于芯片上的实际元件:数字与模拟输入、限幅比较器、一只ADC、一个可编程逻辑阵列,以及一组DAC。与之相比,Anadigm公司讨论芯片时并不采用大多数用户的术语,如电容、可配置放大器、阶梯网络或可编程模拟开关等。该公司描述的是模拟功能块:运放、滤波器,等等。Anadigm公司首席运营官Simon Dickinson表示,当器件将成为一个较大设计中一分子时,该公司有时会鼓励用户把芯片想象成一个功能固定或具有多功能的黑盒子,而不管其中的内容。

一般来说,可编程模拟芯片的功能越专业,则隐喻就更贴切。不过,如果一种可编程结构是高度自适应的,则供应商可以采用两种方案之一:应用与其下架构无关的隐喻,如Verilog-A或Spice网表,或隐藏可编程结构的隐喻,仅将其表述成一个参数化的固定功能芯片。隐喻的重要性在于,是它决定了用户采用的设计方法,而不是其中的硅结构。一些案例可以说明这一点。

一些实例方法

Lattice公司主管电源控制器IC的营销经理Shyam Chandra称:“人们仍然采用分立芯片控制复位信号、看门狗时序,等等。我算了一下,(安森美的产品系列中)仅用于复位生成的就有400种芯片,市场上肯定有100种热插拔控制器IC。”因此Lattice选择了一种编程隐喻方式,使设计者像在使用一些较小型的固定功能芯片。

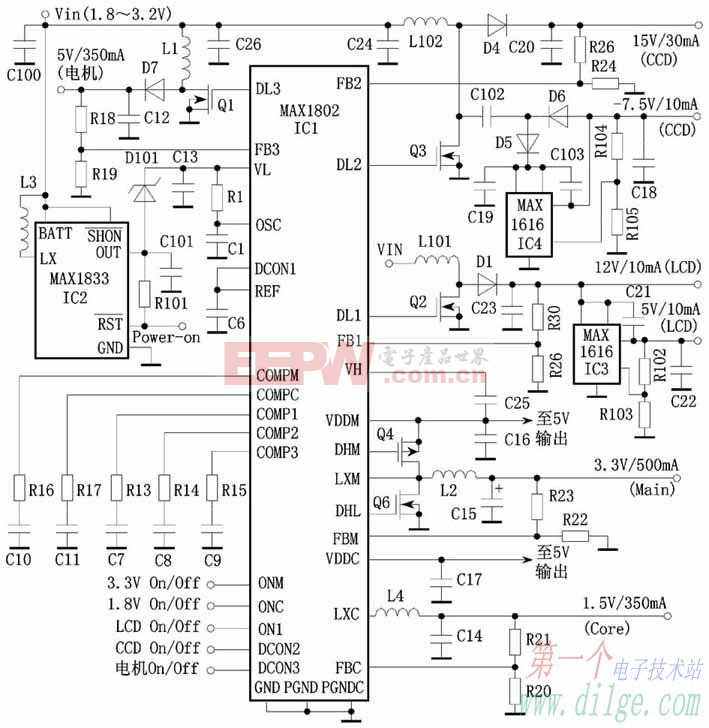

在开发设计规格时,Lattice产品的用户会在数据表中搜索他们电路板上的处理器、内存、FPGA和其它器件,为每只芯片确定所需上电次序。对这些次序作编译,就生成了控制器逻辑的完整状态图。但这是一种手工劳动,Chandra警告说:“大约75%的情况下,第一次工作是不正确的。人会出现错误,数据表规格中也经常会有灰色区域。”因此,Lattice公司提供了一种简单的编程语言和波形仿真工具,用户可以对次序作编码,在不毁坏任何东西的情况下观察其动作。当次序正确时,工具会配置Lattice芯片中的状态引擎,使之可以驱动复位信号和为电路板提供顺序供电的MOSFET门。同样,Lattice公司还提供了一个辅助工具,用于设置芯片的微调与容限检测电路。通过使用一个已知DC/DC转换器的库,软件可获取用户的容限和电压要求,设定片上比较器与DAC以及所需电阻值,同时监控转换器的输出和驱动微调输入。

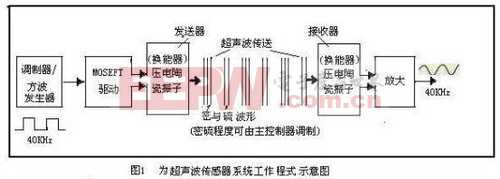

标准产品隐喻的概念超出了电源控制领域。在一个不同的市场中,Actel公司提供在Fusion系列FPGA上的可配置AFE(模拟前端)块。该公司也同样支持其可编程模拟段的配置,但也同样怀疑用户对板级仿真的兴趣。该公司一名现场应用工程师Mark Nagel说:“我得说,我们只有不到一半的客户会做任何一种全电路板仿真。在芯片级,我们确实提供了一种工具,它可以为模拟激励生成波形,然后将其送入一个ADC模块,提供用于FPGA逻辑ModelSim仿真的数字输出。不过我们的AFE结构相当固定。对大多数人来说,我们的用户倾向于先考虑分辨率、采样率等的需求;配置AFE,并作尝试。你可以用板上元件查询AFE中的模拟结点,可以用芯片FPGA部分中的一个Synplicity嵌入逻辑分析仪查看数字输出。”因此,用户一般不用仿真工具研究AFE;他们只仿真数字逻辑部分。

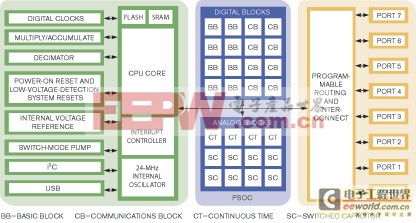

图2,Cypress公司的PSoC包含一个微控制器,以及模拟与数字块组成的可编程阵列。

另外一个例子来自Cypress半导体公司,其PSoC(可编程系统芯片)提供相对丰富的可配置模拟元件阵列,它与一个数字构建块和一个微控制器核心紧密耦合(图2)。Cypress硅结构的通用特性可以确定一种高级语言隐喻,以及一种综合仿真设计流。不过该公司选择了一个不同的方向。Cypress公司现场应用工程师Jason Baumbach解释说:“我们的隐喻法是一个部件目录,而不是一个可编程模拟阵列。给用户展示数千个寄存器对他们没有帮助。我们是提供一个‘用户模块’的目录,”即芯片上可配置的模拟阵列部分。不过,它们对于用户来说就是现成的模拟部件。用户根据用户模块绘出其设计的模拟部分的逻辑,然后采用Cypress PSoC开发环境,就可以直接从逻辑图进入到试验板阶段。Baumbach称:“我们并未看到很多人在使用Spice或Matlab。多数情况下,他们尝试做的模拟电路都相当简单。”

评论