FPGA与ADSP TS201的总线接口设计方案

2.1 32位数据总线,32位寄存器,写操作

前面提过,DSP采用流水协议写FPGA时,流水深度固定为1,FPGA在前一时钟沿采到地址、WRx信号有效,在下一时钟沿就锁存数据,如图3所示,FPGA在时钟沿1采到地址总线上的地址与寄存器地址一致,WRx信号为低,写标志信号S_W_FLAG置高,由于采用同步设计,FPGA只有在时钟沿2才能采到S_W_FLAG为高,一旦采到S_W_FLAG为高,FPGA就锁存数据总线上的数据,即在时钟沿2锁存数据。

2.2 32位数据总线,32位寄存器,读操作

与写寄存器不一样,读寄存器时流水深度在1到4之间可设,需要注意的是,为避免总线冲突,

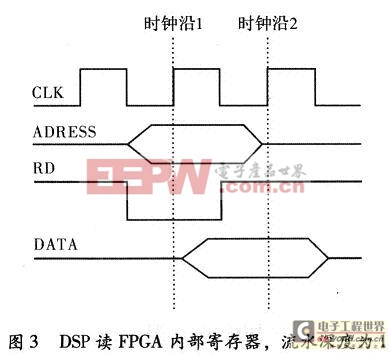

如果流水深度设置为1,FPGA在前一时钟沿采到地址、RD信号有效,应确保在下一时钟沿数据已经稳定的出现在数据总线上,否则DSP不能正确读取数据,如图3所示,在时钟沿1采到地址总线上的地址与寄存器地址一致,RD信号为低,驱动数据总线,在时钟沿2数据已稳定出现在数据总线上,DSP可以读取。

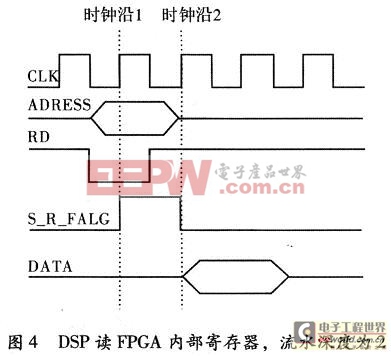

如果流水深度设置为2,FPGA在前一时钟沿采到地址、RD信号有效,应确保隔一时钟周期后,数据稳定的出现在数据总线上,这样就像写操作一样,需要加一个标志,当条件满足,标志为高,一旦标志为高,输出数据,如图4所示。

综上所述,流水深度加深一级,FPGA就晚一个时钟周期驱动数据总线。可以看出,虽然流水深度在1~4之间可设,但是总能保证一个时钟周期传输一个数据。

评论