采用CPLD来替代微处理器的6种方法

脉冲宽度调制

一般而言,设计人员针对某一功能选择一款微控制器,例如脉冲宽度调制(PWM),这些功能也可以采用CPLD来实现。在PWM中,方波的时间周期不变,而信号保持高电平的时间在变化或者受到调制。这样,信号的占空比(tON)是变化的。PWM为数字系统中的

CPLD并没有专用PWM电路,但是实现PWM输出并不难。例如,MAX IIZ CPLD的内部振荡器可以用作频率源,计数器可以用于调制所产生的频率。

模数转换器

设计人员经常选择微控制器来实现模数转换器(

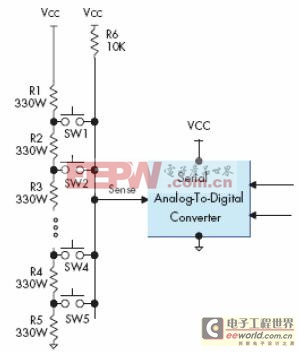

图2所示为一个基本开关阵列和ADC。在VCC和GND之间串联了一组电阻,每个电阻抽头和公共极上连接了一个开关。如果开关接通,电路产生一个和电阻堆中开关位置成比例的电压信号。要在数字系统中使用,模拟信号必须转换为数字值,通常选用含有内置ADC的微控制器来实现这一功能。

图2.模拟键盘阵列

然而,CPLD也是一种选择。加入一个简单的低成本外部电容后,MAX IIZ CPLD可以利用其内部振荡器、施密特触发器I/O以及高密度算法可编程逻辑架构来完成模数转换(1)。

上电排序

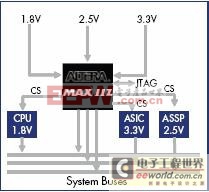

MAX IIZ器件针对大量的系统管理功能进行了优化,例如多电压系统上电和系统复位上电排序功能,以及片选信号生成等。这两类应用一般集成在一个非易失、瞬时接通器件中。多电压系统上电排序功能需要采用瞬时接通器件,该器件能马上管理PCB上其他器件的上电顺序。因此,相对于在毫秒量级上电的微控制器,能够在几微秒内上电的CPLD是上电排序功能更好的选择。

图3所示为典型的MAX IIZ器件上电排序应用。随着电路板密度以及电路板电源层数的增加,上电排序变得越来越复杂。MAX IIZ CPLD能够轻松管理系统复杂程度不同的上电排序。多电源供电支持不同的器件,需要采用控制逻辑来管理每一器件的上电顺序。为确保在上电期间不会出现对总线信号的意外驱动,也需要MAX IIZ器件来控制关键总线信号,直至上电完成。JTAG端口监视上电顺序,存储上电时的错误和信息。它还可以用于在调试阶段设置上电排序断点。

图3. 利用CPLD实现上电排序

评论