基于SOPC技术的内存映射型LCD控制器设计

2.2 寄存器模块(register_bank)

该模块为Avalon总线从端口设备,可以通过NiosⅡ

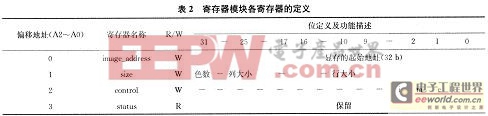

寄存器模块中共定义了4个寄存器;显存起始地址寄存器、显示参数寄存器、控制寄存器和状态寄存器。各寄存器的读写控制、定义及功能描述如表2所示。

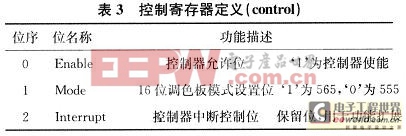

其中,显示参数寄存器(size)中“色数”标志位,值为1表示8位颜色显示,值为0表示16位颜色显示。状态寄存器(status)大小为两位,可与控制寄存器中的中断位(Interrupt)配合使用,为保留位。控制器寄存器的定义如表3所示。

2.3 数据缓存模块(line_buffer)

该模块设计采用了双口RAM,由MegaWizard Plug-In Manager生成,其存储空间约为一行数据所占的空间,用于暂存显示数据。由于DMA不是直接将显存中的数据传给时序发生器,而在中间使用了双口RAM做数据缓存,这样DMA和时序发生器的读、写时序不必严格对应,简化了结构设计。同时,用于16位彩色显示时,可通过数据缓存模块将总线32位的数据输入变为16位的数据输出给时序发生器;而在8位彩色显示时,可通过数据缓存模块将32位输入变为8位输出,实现了数据位数的转化,方便的时序发生器内部的数据操作。

2.4 DMA模块(image_dma)

该模块为Avalon总线主端口设备,它负责向Avalon总线提供有效的地址、数据和写请求信号,并在时钟上升沿发起总线传输,读取显存中的数据;同时,DMA模块产生写数据缓存的地址和数据,将显示数据正确地从显存传送到数据缓存。DMA模块为三状态的状态机,包括空闲状态、传输状态、等待状态,各状态机逻辑关系如图3所示。

评论