一种以CPLD为核心处理电路的数字电压表设计

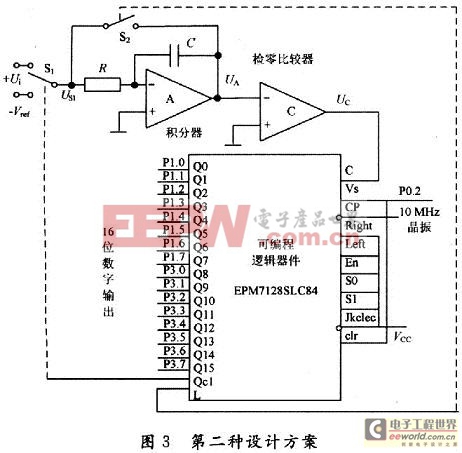

1.2 方案二

采用EDA可编程逻辑器件把16位J-K触发器组成的计数器和控制电路集成到系统内部,不仅可以消除外界干扰,减小测量误差,且大大节省空间,提高系统的响应速度。CPLD使用方便、快捷,性价比很高,如图3所示。

对比两种方案的性能,本设计选用方案二。

2 系统设计

2.1 硬件部分

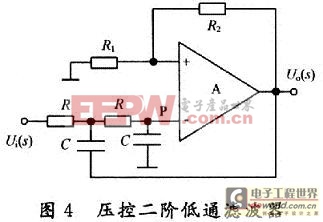

2.1.1 滤波电路

滤波电路采用压控二阶低通滤波器,如图4所示。运放采用低温漂高精度运放OP07,取R1=R2=R=1.592 kΩ,C1=C2=10μF,则f0=10 Hz。

传递函数为:

![]()

当Aup3时,电路才能正常工作,不产生自激振荡。令:

![]()

则电压放大倍数:

![]()

对直流信号的放大倍数为:

![]()

评论