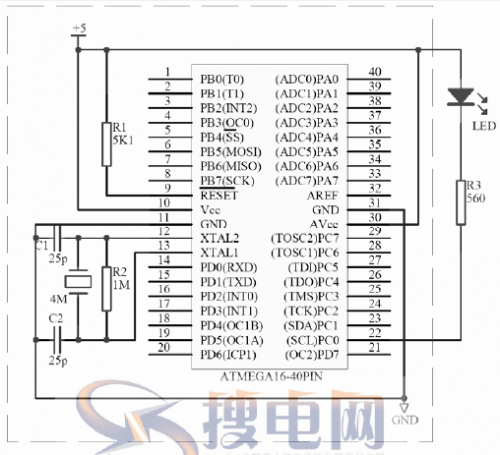

基于AVR和CPLD的高速数据采集系统的设计

2 程序设计与实现

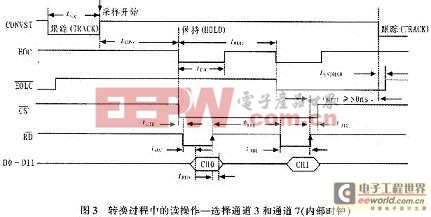

编程实现采集部分的功能,采集部分时序图如图3所示。任意选择两条通道进行内部时钟分析,图中为第3通道和第7通道,当控制信号产生低电平时,控制引脚起作用,触发采集功能,同时EOC引脚电平至低。在tCTR段时间后读信号被启动经过tACC的时间后,12位数据将出现在DO-D11引脚上。在整个采集、存储过程中其他通道和通道3、通道7一样,随后将数据存入数据缓存器中。

2.1 控制A/D转换程序设计

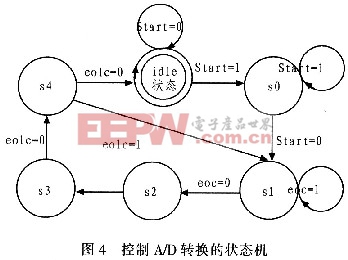

根据控制存储的要求,首先要设计控制A/D转换的状态机,用来确定A/D转换的状态,根据MAXl308工作时序特点而设计的控制A/D转换的状态机转换图如图4所示。实现控制A/D转换的状态机部分主要VHDL程序源代码如下:

评论