基于PSoC3的多通信接口时的DMA设计

一、 Cypress PSoC3芯片介绍

Cypress PSoC3使用基于单循环流水线的高性能8051内核 (67MHz/33MIPS),提供业界广泛采用的5.5V至0.5V电压范围和低至200nA的休眠电流,可以满足极低功耗的应用场合。PSoC3的高性能模拟子系统和数字系统都拥有可编程通路,允许将任何模拟或数字信号(包括可编程时钟)分配到任何通用I/O引脚,这为使用者提供了真正的“系统级”可编程能力。

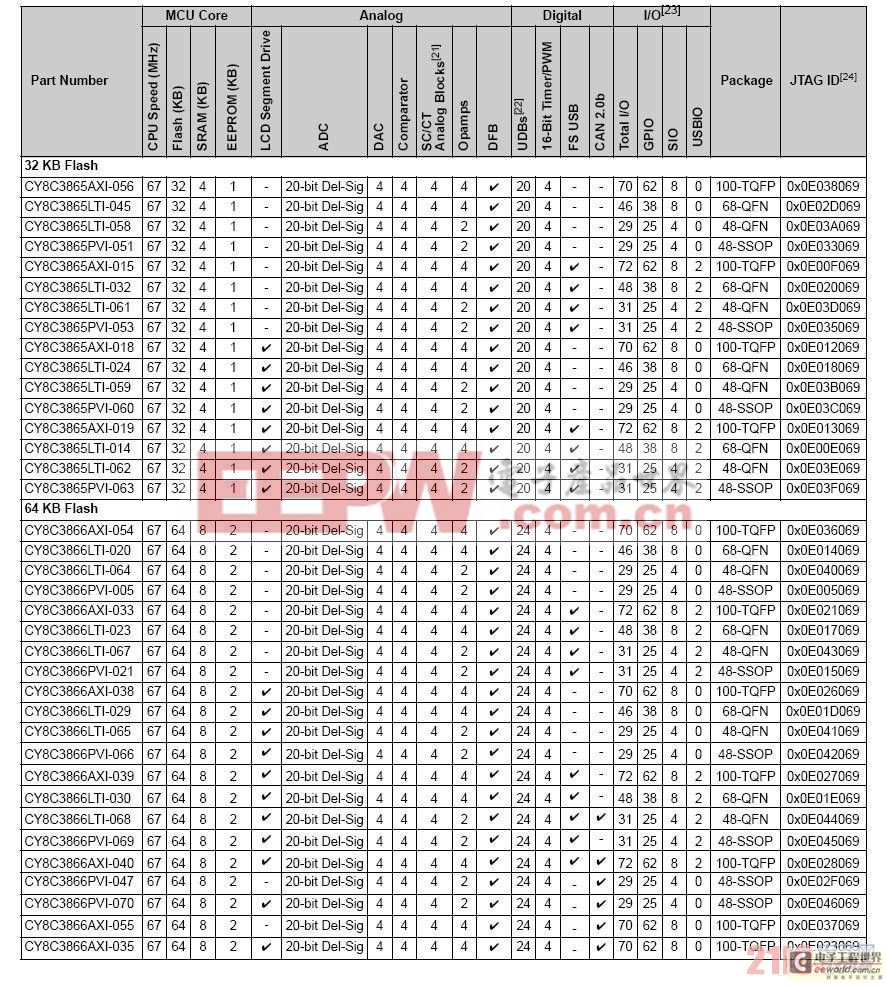

Cypress PSoC3的芯片编号是CY8C38xx,该系列芯片依据功能模块的不同包含多种芯片。表1是CY8C38xx系列的选型指南,除了表中列出的特性外,每个CY8C38xx芯片还包含:1.024V±0.1%的精密片上电压参考源,带PLL的1~66MHz±1%的精密可编程时钟源,有ECC(错误校正码)功能的Flash,DMA(直接存储器访问),4KB可调试跟踪的RAM,JTAG/SWD编程/调试接口,支持片外存储器访问等。

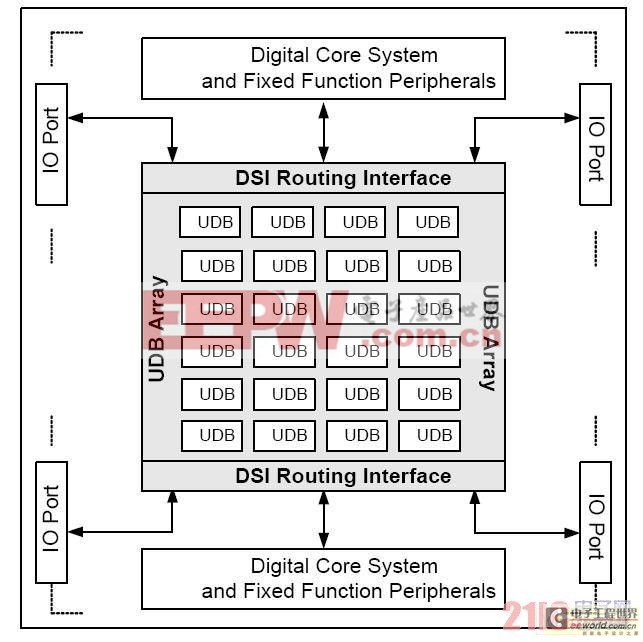

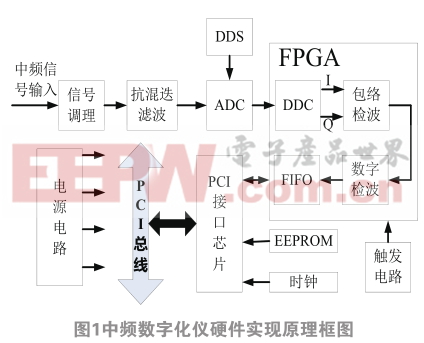

Cypress PSoC3 内部采用CPLD的结构实现了完全的数字可编程电路。图1显示了CY8C38xx系列内部的可编程逻辑图。从图1中可以看出,外设和逻辑部分可以彼此互联,也可以连接到任何引脚。数字可编程逻辑包括了以下部分。

UDB(Universal Digital Blocks)形成了可编程数字系统的核心功能,由PLD和Data path组成,可以创建各种通用外设和定制化功能。

UDB Array由多个UDB通过矩阵和可编程互联组成,支持UDB和DSI(Digital System Interconnect)之间很灵活的扩展。

DSI是数字信号的集中互联,包括UDB,固定功能外设,I/O,中断,DMA和其它部分的数字信号。

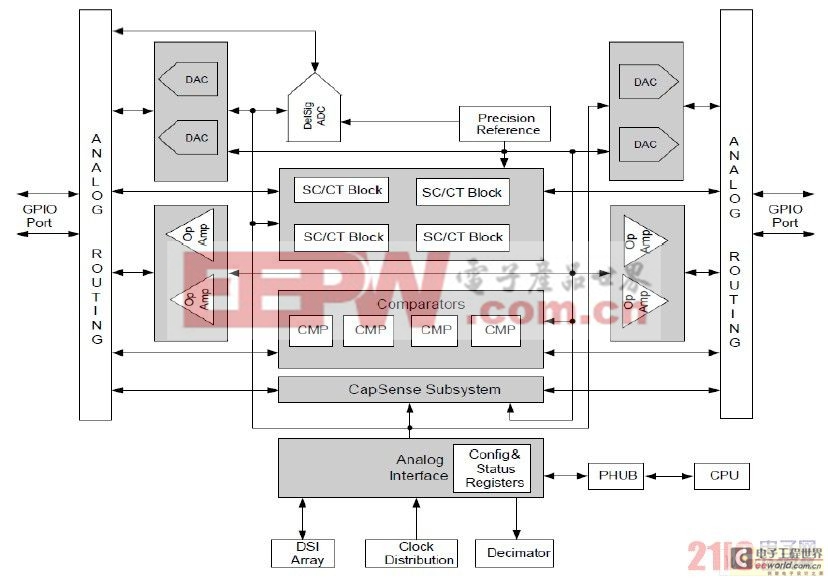

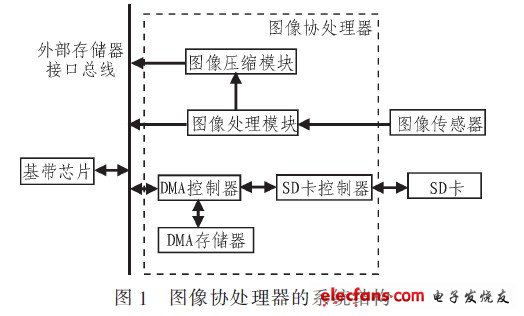

强大的模拟资源以及灵活的模拟布线资源也是PSoC3的一大亮点之一。图2是CY8C38系列芯片的片内模拟资源图,通过这些可编程的模拟电路,可以构成标准的模拟信号处理模块。并且这些模拟资源可以通过内部的模拟互连子系统进行连接,提供高度的模拟设计自由度以及IP资源的保护。模拟子系统有以下系统构成。

·有模拟全局和局部总线,模拟开关构成的高度可配置的结构。

·高精度的Delta-Sigma ADC.

·支持8位的电压或者电流DAC.

·四路比较器并且可以有选择性的互联到LUT中.

·多达四个的SC/CT模块可以构成OPAMP等模拟电路

·多达四个内部的OPAMP,可以连接到GPIO作为大电流输出的缓冲器。

·CapSense子系统支持电容触摸的检测。

·内部高精度参考电压源。

图1 CY8C38系列芯片的片内可编程数字系统图

表1 PSoC3 选型指南

图2 PSoC3 内部模拟资源图

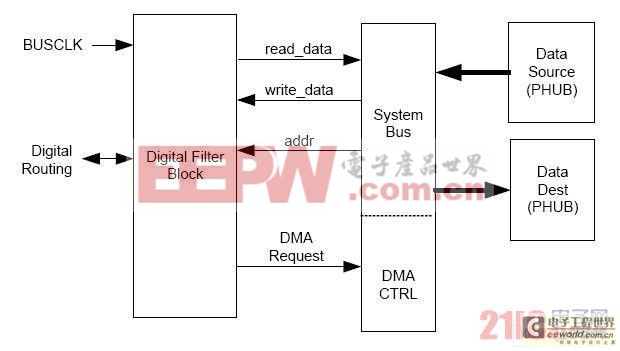

除了模拟和数字可编程逻辑外,CY8C38 系列芯片都包含了一个专用于数字滤波的硬件加速器DFB(Digital Filter Block),它内部的专用乘法器和加速器可以在一个系统时钟内计算一个24 位数与24 位数的乘法。使用DFB 可以方便的实现FIR 和IIR 数字滤波器,而且几乎不占用MCU 的资源。在实现滤波器之外,DFB 还可以作为PSoC3 的算法加速器,可以很方便快捷的实现各种数字算法,而且不需要占用PSoC3 的CPU 资源。

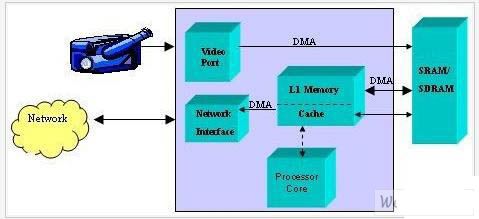

图3 是DFB 的模块框图,典型应用是将某个片内数据源(例如ADC 或某个DMA)的数据连接到DFB,经DFB 处理后将结果输出到另一个片内数据源(例如DAC 或另一个DMA)。数据的移入和移出可以设定由特定的DMA 控制,也可以由MCU 直接移动。

图3 DFB 结构图

除了可编程的资源之外,PSoC3内部还提供了特定功能的模块。这些模块可以不占用模拟,数字可编程以及MCU资源,完成相应的功能。这些模块包括:

·支持高达1MBPS的Can总线控制器,兼容ISO-11898-1标准。

·全速USB2.0控制器,支持8个端点和DMA数据传输控制。

·支持50k/100k/400k/1M BPS的I2C主/从总线控制器,兼容Philips ‘The I2C Specification’ Version 2.1。

·16 Bit专用的定时,计数和PWM等常用的嵌入式系统模块。

二、 Cypress PSoC®Creator™ 集成开发环境

Cypress PSoC Creator 开发环境是Cypress 为PSoC3 / PSoC5可编程片上系统提供的高效,易用的继承开发环境。

该独特的新型设计软件使得工程师能够按照自己的思维方式进行设计。使用基于电路图的方式完成对可编程模拟,数字以及布线资源的设计。该软件还提供了特有的嵌入式系统的组件库来应用其内部的资源,通过在组件库中选择组件并使用基于电路图的方式可以使得整个开发过程就像搭积木一样,简单高效的实现工程师的设计。该软件工具通过电路综合可以自动的把用户的设计转化成对可编程电路的配置,使得用户即使不了解芯片的细节也可以完成复杂的电路设计。使用PSoC Creator进行设计的时候,客户是根据应用需求急性设计,而不是目标器件的限制。重新构建设计就像修改程序一样,不需要复杂的电路板级修改。

PSoC Creator将一个最新的软件开发IDE与一个*性的图形设计编辑器结合在一起,构成一个独特的强有力的软硬件同步设计环境。它提供内容丰富的、存有几十个预先配置过的模拟和数字外设库,可以方便地拖放进电路图设计界面并组成强大的系统。该工具还可以自动为所有片上信号分配管脚,如有需要,甚至还能将I/O分配到最佳管脚。每个外设元件的参数均经过仔细的配置,以保证应用效果能最好地满足设计者的要求,且没有资源浪费。构建过程会为每一个元件产生一个一致的、容易记住的API系列,这样,软件开发者即可控制硬件,而无需为基本执行指令操心。 定制的设计及其相关的API还可以方便地存储在库中,用于将来的项目或在组织内部分享。

PSoC Creator内部包含了全功能免费的编译器,其独特的综合布线工具能够自动综合客户的设计输入,并生成相应的API。PSoC3的工程采用了工业界常用的Keil CA51编译器,而GNU GCC-ARM编译器也包含其中,能够针对PSoC5的设计进行编译。在综合,编译等完成之后,生成兼容Intel Hex格式的配置文件对芯片进行配置。

评论