基于FPGA的基带64×64数据分配矩阵设计方案

3.2.2 译码模块设计

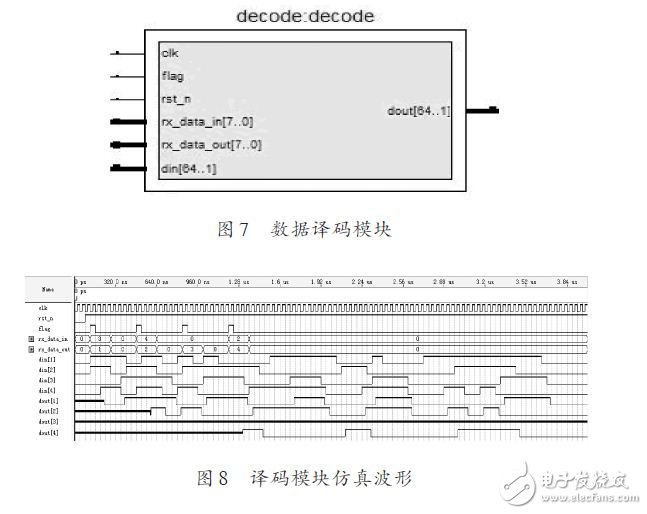

本文引用地址:http://www.eepw.com.cn/article/221565.htm译码模块的模块化框图如图7所示,其功能是对上位机发送的输入输出端口编号进行译码,使相应的输入端口和输出端口连通,如检测到flag 有效的情况下,rx_data_in为2,rx_data_out为3,则该模块会将din[2]通道的输入信号经dout[3]输出通道输出。部分代码如下[10]:

![则该模块会将din[2]通道的输入信号经dout[3]输出通道输出。部分代码如下[10]:](http://editerupload.eepw.com.cn/201402/98f23960cbfc37a6c4c0aa38b05dfbbc.jpg)

3.2.3 译码模块仿真

由于64×64的仿真很繁琐且不易操作,所以对4×4的译码模块进行仿真,仿真结果如图8所示,输出1与输入3相连,输出2与输入4相连,输出3悬空,输出4与输入2相连。

4 结语

本文采用FPGA作为实现控制逻辑的核心部件,提出了基于FPGA的基带64×64 数据分配矩阵设计方案,并介绍了上位机的软件设计思路和FPGA的内部编程实现及仿真。经验证本系统基本能实现基带数字信号的分配路由,从而证实了该方案具有规模大、成本低、高速等特点,可广泛应用于大规模基带数字系统测试及信号程控分配调度中。

fpga相关文章:fpga是什么

晶振相关文章:晶振原理

评论