基于FPGA的多普勒测振计信号采集与处理系统设计方案

2.2 FPGA逻辑设计

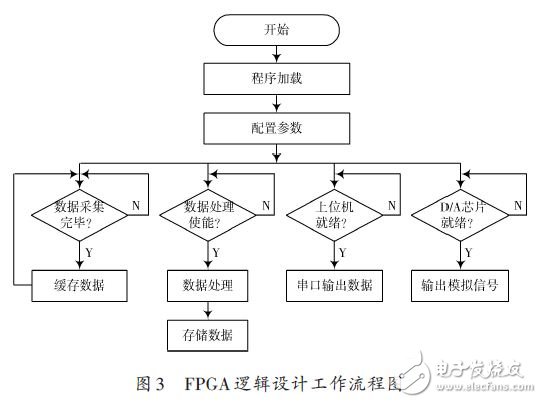

本文引用地址:http://www.eepw.com.cn/article/221564.htm在FPGA逻辑设计中,采用Altera公司的Quartus Ⅱ综合开发环境对FPGA进行设计、仿真和调试,实现信号的采集和处理功能,FPGA逻辑设计工作流程图如图3所示。

在工作过程中,FPGA首先检测是否接收到数据采集完毕的使能信号,如果没有接收到就一直进行检测,如果收到就读取16 位数据并缓存。当FIFO 接近全满状态时启动数据处理逻辑,数据处理逻辑通过一系列乘加运算结合流水线的设计方法实现,并将运算结果适当截位输出给双口RAM.双口RAM 拥有两套完全独立的数据线、地址线和读写控制线,当检测到有数据输入时,读地址开始加1,否则读地址保持不变。上位机准备就绪,即双口RAM 数据准备输出时,双口RAM 写地址开始加1,通过串行接口将数据输出。在输出模拟信号时,只有当DAC8551芯片输入寄存器接收到24位数据,同时同步信号为低电平时,才能启动 D/A转换逻辑。

下面将介绍几个典型数字逻辑模块的关键设计点。

(1)时钟模块

本设计中外部晶振提供给FPGA的时钟为50 MHz,时钟模块的功能就是根据设计要求,利用锁相环以及使能时钟的设计方法为各个模块提供所需的时钟信号。通过锁相环配置工具将50 MHz的系统时钟进行1/2分频,从而产生频率为25 MHz并满足时序约束的主时钟。使能时钟设计,即不增加新的时钟,而只是利用原有主时钟,让分频信号作为使能信号来使用,通过该设计对主时钟进行1/16 分频,为信号处理模块提供工作时钟。

(2)A/D逻辑模块

A/D 逻辑模块的任务是根据ADS1174 的转换时序图,在芯片的引脚发出或接收相应的信号,使得ADS1174完成启动、配置和数据读取操作。其控制操作如下:首先配置ADS1174 的相关参数,包括运行模式、接口类型等,然后通过查询ADS1174的DRDY信号来判定数据转换是否完成,开始读取数据,最后将读得数据进行串并转换,同时完成数据的缓存。A/D逻辑模块每完成一次信号采样,则等待下一次触发脉冲的到来。

(3)数据处理模块

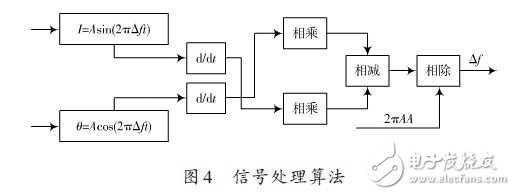

数据处理模块的功能是提取出多普勒测振计信号中的频移信号,本设计采用如图4 所示的信号处理算法,通过微分和乘加运算,同时结合流水线的设计方法来实现。微分运算的处理是将前一个数据延迟一个单位时间,用当前的数据减去前一个数据得到的。通过宏模块构建16 b × 16 b有符号乘法器来实现乘法运算,同时为了避免溢出,对乘法运算结果适当截位。相关除法器操作则与乘法器类似。

电子管相关文章:电子管原理

光耦相关文章:光耦原理

fpga相关文章:fpga是什么

评论