基于FPGA的帧同步系统设计方案

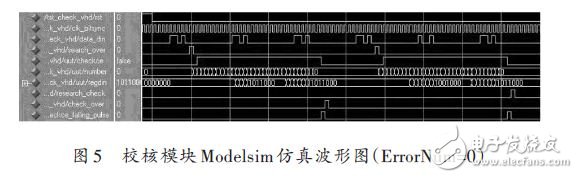

图5 是校核模块的Modelsim 仿真波形。其中,帧长度LenFrame=16,校核帧数CheckNum=2,容错门限ErrorNum=0,其余参数与搜索模块相同。从波形上很容易 看出,当search_over第一次出现高电平时,其后连续两组同步码均为“1011000(ErrorNum=0)”;当search_over第二 次出现高电平时,其后第一组同步码为“1001000(ErrorNum=1)”,第二组同步码为“1011000(ErrorNum=0)”。因此第一 次帧校核顺利通过,校核完成后check_over输出一个高电平脉冲,research_check保持为低电平;第二次校核未通过,校核完成后 research_check输出一个高电平脉冲,check_over保持为低电平。

本文引用地址:http://www.eepw.com.cn/article/221559.htm

2.4 同步模块的VHDL设计与仿真

为了简化设计,将同步状态分为三个进程来完成,即计数器进程(Counter)、帧校验进程 (FrameChecking)和同步校验进程(SyncChecking)。Counter 进程用于产生帧内数据位置的计数,当检测到check_over 信号为高电平时,重新开始以帧周期(LenFrame)循环计数;FrameChecking 进程用于产生帧起始位置的同步脉冲,且高电平脉冲与同步码的最后1 b对齐,该进程首先需要对同步码组进行校核,如校核通过,则在同步码位置处产生一个高电平脉冲FramePosition,如果校验未通过,则在同步码位 置不产生高电平脉冲;SyncChecking进程通过判断FramePosition 来确定系统是否处于同步状态,即只需判断FramePosition是否连续在同步码组的位置出现低电平,如连续出现SyncNum 次低电平,则判断为失锁,否则继续维持同步状态。

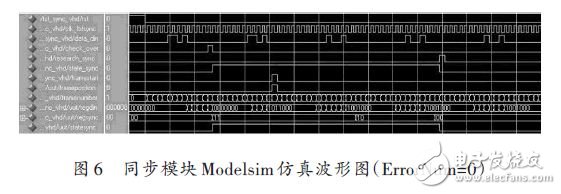

图6 是同步模块的Modelsim 仿真波形。其中同步态校核帧数SyncNum=2,其他参数与校核态相同。从图中可以看出,当检测到check_over为高电平时,计数器Number 开始以周期为帧长LenFrame=16循环计数。当check_over 出现高电平时,其后连续4 组同步码为 “1011000(ErrorNum=0)”,“1001000(ErrorNum=1)”,“1001000(ErrorNum=1)”,“1001000(ErrorNum=1)”。 由于此时设置的容错门限ErrorNum=0,因此第一帧同步码校核通过,输出了同步脉冲FramePosition,此后出现连续3 个校核未通过的数据帧。同步状态信号State_Sync 高电平状态持续维持了2 帧数据的长度,而后停止同步状态,输出失步信号research_sync,用于启动搜索过程。

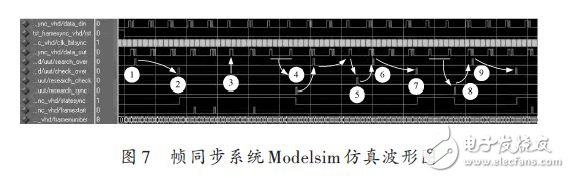

本实例的目标器件为XC3S200-4FT200,FPGA实现后,查找表资源(LUTs)占用了 484 个(12%),全局时钟资源(GCLKs)占用了1个(12%)。最高系统时钟频率(Maximum frequency)可达54.81 MHz.图7 是帧同步系统的Modelsim 仿真波形。其中,各模块的容错门限ErrorNum均为0,其他同步参数不变。

图7 实际上对帧同步系统的搜索、校核、校核未通过、失步、重新搜索、重新同步等过程进行了完整的仿真测试。

4 结语

本方案是基于模块化设计思想,采用VHDL语言对帧同步系统进行设计实现,有利于程序的移置及维 护。方案设计的关键在于理解各模块之间的信号接口关系及时序关系。在模块设计时,通过进一步合理划分模块内部的结构,可以更好地理清程序思路并提高设计方 案的效率。最后利用Modelsim 6.0软件进行了仿真测试。仿真结果表明,该方案中设计的同步系统工作稳定,满足性能要求。

fpga相关文章:fpga是什么

评论