一种通用数据采集系统的设计方案

2.5 电气隔离设计

本文引用地址:http://www.eepw.com.cn/article/221483.htm由于该系统为模拟/数字混合信号系统,电路中的噪声会对数模和模数转换精度造成影响,因此在电路的实现上应该对板卡芯片进行降噪和隔离保护,这样既避免了不同信号之间的相互影响,提高了系统的共模抑制能力,也使得一些比较昂贵的芯片不会因为外部信号的不稳定而烧毁。

传统的隔离方式是对每个通道都使用电容耦合模拟隔离芯片ISO124等进行隔离。这类隔离方式其输入和输出分别由两组直流电源供电,而且存在较大的漂移,输出信号通常存在纹波,尤其当信号比较小时,输出的相对误差会增大。因此,还需要对输出信号进行滤波、调零等调理措施,使得系统电路比较复杂。

光电耦合器性能优越,具有良好的抗干扰能力,因而被广泛地应用于输入和输出信号的电气隔离。使用HCPL2630 等高速光耦进行光耦隔离,只需要一组直流供电电源,电路十分简单。其良好的电绝缘能力和抗干扰能力使得模拟地和数字地分开,消除了共模电压影响。系统选用串行而非并行的ADC和DAC,只需要隔离三路的SPI总线数字信号,这样进一步简化了电路设计。

3 软件设计

3.1 FPGA逻辑

FPGA智能板卡是整个数据采集系统的核心,由其产生和发送DAC与ADC的SPI接口和工作时序。其内部的逻辑单元主要包括:DAC 控制器、ADC 控制器、接口单元等。DAC 和ADC 控制器是FPGA 内部的主要执行单元,它按照DAC和ADC工作时序进行相应的工作。

DAC 控制器:对于发送过程,在建立周期,DAC 控制器初始化控制信号CS(置“1”);在命令周期,使能CS信号(置“0”),同时按照时钟节拍,将16 b 命令字以串行方式发送至DAC;在采样周期,对CS信号进行保持;转换周期,置位CS信号(置“1”);对于接收过程,在建立周期LDAC处于锁定状态(置“1”);在接收周期,以串行方式接收上次转换的16 b数据;在存储周期,控制器将LADC置“0”,改变寄存器内容;在空闲周期,复位LADC(置“1”)恢复寄存器的锁定状态。

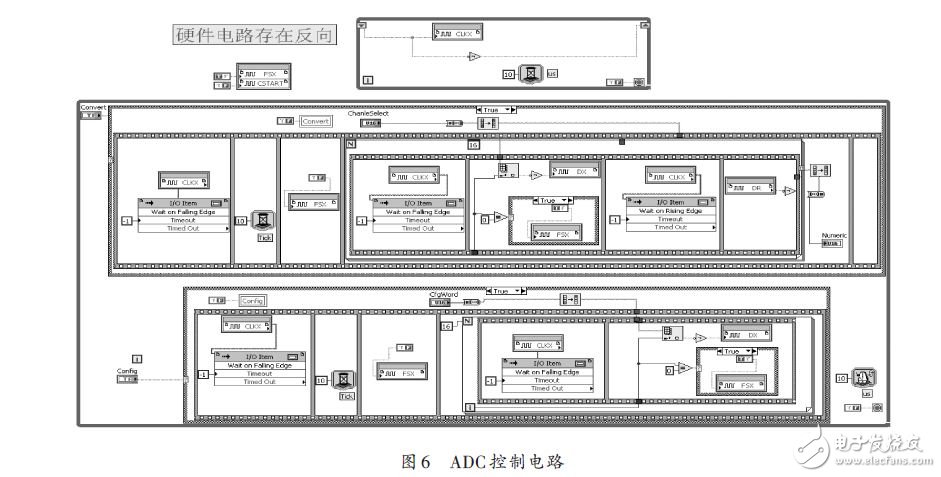

ADC 控制器:对于发送过程,在建立周期,ADC 控制器初始化控制信号CS(置“l”);在命令周期,使能CS信号(置“0”),同时按照时钟节拍,将16 b 命令字以串行方式发送至ADC;在采样周期,对CS信号进行保持;在转换周期,置位CS信号(置“1”),并载入下一通道的命令字,同时,计算下一次接收数据的存储地址。对于接收过程,在建立周期,控制器清零各接收寄存器,同时复位内部RAM的写信号WR(置“0”);在接收周期,控制器按照时钟节拍,接收ADC 上一次转换的14 b 串行数据;在存储周期,控制器使能WR 信号(置“1”),并将接收到的数据写入ADC通道对应的RAM 单元;在空闲周期,控制器复位WR信号(置“0”)。

3.2 LabVIEW程序设计

根据FPGA内部的逻辑单元结构和功能,通过NI公司的LabVIEW图形化编程开发平台对上述逻辑进行了设计,并进行了功能仿真。给出ADC 控制器LabVIEW程序实现,如图6所示。

NI公司的LabVIEW 图形化编程开发平台具有一系列的优点,它不同于VHDL等基于时序的语言,而是一种基于信号流向的语言,程序运行过程和真实硬件电路运行原理相似,用LabVIEW编程的过程就像设计电路图一样。另外它有不需要预先编译就存在语法检查和调试过程使用的数字探针,其丰富的函数、数值分析、信号处理和设备驱动等功能,都是十分优越的。LabVIEW将广泛的数据采集、分析与显示功能集中在了同一个环境中,可以在自己的平台上无缝地集成一套完整的应用方案。

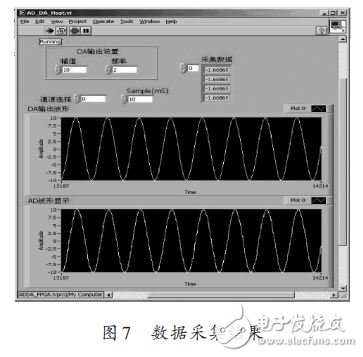

将由LabVIEW 图形化编程开发平台通过FPGA 生成的正弦信号经D/A 电路输出,经过A/D 电路进行采集。分别选定四路不同的D/A 通道和A/D 通道进行输出和输入显示,图形一致,程序运转正常,波形显示清晰。限于DAC 和ADC 转换速度,采集到的波形存在着微小的相位延迟。如图7所示。

4 结语

基于NI公司FPGA 板卡的通用数据采集系统方案的设计与实现。通过实例证实了该系统可靠性、实时性、快速性比较好,使得数据处理能力得到了极大的提高,可完全胜任大容量、高精度数据的高速采集。对于采集到的信号可以进行实时处理或保存,也可通过串行口将其送至上位机进行后续分析处理。对于不同应用场合,在FPGA的逻辑单元足够的情况下可以很简便地依据实际情况对其做相应调整,具有较强的通用性,实用价值比较高。

光耦相关文章:光耦原理

评论