基于FPGA多路机载冗余图像处理系统的设计方案

2.1 SDRAM选择依据

整个系统显示的分辨率为1600×1200@60 Hz,信号位为真彩色24b,则一帧图像所需需要存储的容量C = 1 600×1 200×24=46 080 000 b≈47 Mb;考虑到SDRAM乒乓操作和容量等问题,选用MICRO公司生产的容量为128M的MT48LC4M32B2TG-6器件,速度等级6,时钟频率达到166 MHz.该器件具有32根数据线和12根地址线,还有一些控制线。通过在FPGA内部搭建逻辑控制单元,可以很好的控制SDRAM 视频信号的翻转等操作。

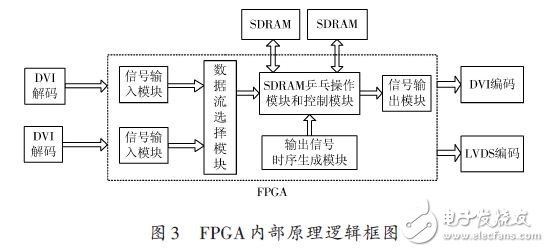

2.2 FPGA内部原理逻辑框图

FPGA内部原理逻辑框图如图3所示。

2.2.1 FPGA内部逻辑功能介绍

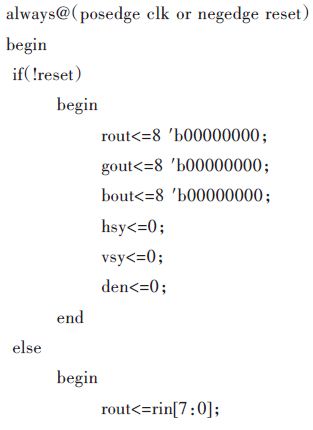

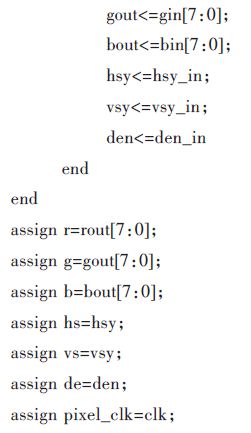

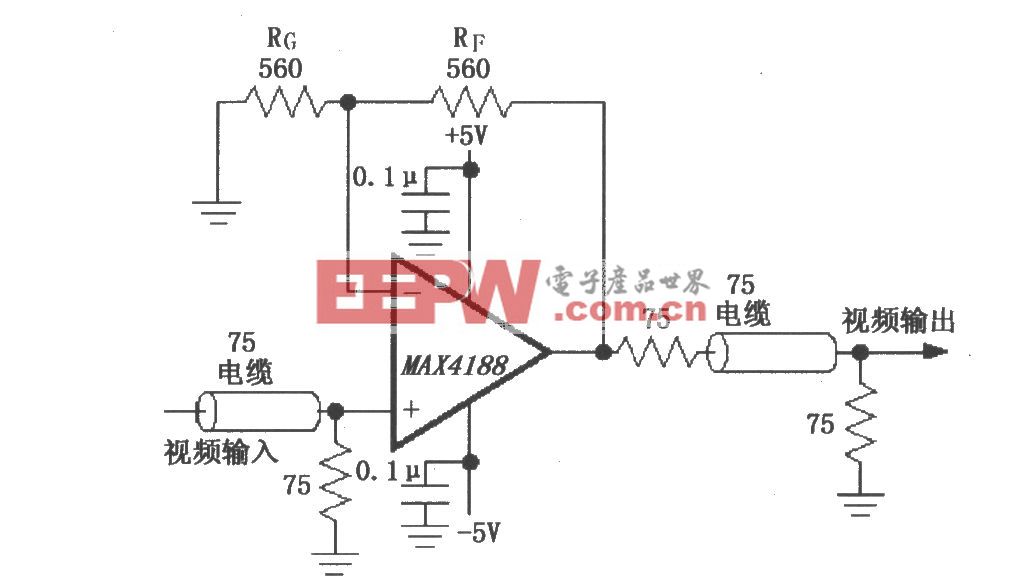

(1)信号输入模块

这部分的主要功能是接收外部输入的视频信号,增强输入信号的驱动能力,为信号的后续处理做准备。其用Verilog 语言实现的逻辑代码如下所示:

评论